Synergistic Processor Unit Instruction Set Architecture

Version 1.2

January 27, 2007

© Copyright International Business Machines Corporation, Sony Computer Entertainment Incorporated, Toshiba Corporation 2006, 2007

All Rights Reserved Printed in the United States of America January 2007

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM PowerPC IBM Logo PowerPC Architecture ibm.com

Cell Broadband Engine is a trademark of Sony Computer Entertainment Incorporated.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com

The IBM semiconductor solutions home page can be found at ibm.com/chips

Version 1.2 January 27, 2007

# Contents

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                                |

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                                                |

| Who Should Read This Document                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                |

| Related Documents                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

| Document Organization                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| Version Numbering                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

| How to Use the Instruction Descriptions                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

| Conventions and Notations Used in This Manual                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

| Byte Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

| Bit Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

| Bit Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

| Instructions, Mnemonics, and Operands                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| Referencing Registers or Channels, Fields, and Bit Ranges                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                   |

| Register Transfer Language Instruction Definitions                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |

| Instruction Fields                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                                                                                                                                                |

| Instruction Operation Notations                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                |

| Revision Log                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                   |

| 2. SPU Architectural Overview                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

| 2.1 Data Representation                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

| 2.2 Data Layout in Registers                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

| 2.3 Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                |

| 3. Memory—Load/Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

| 3. Memory—Load/Store Instructions<br>Load Quadword (d-form)                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b> 31</b>                                                                                                                                        |

| Load Quadword (d-form)                                                                                                                                                                                                                                                                                                                                                                                                                            | <b> 31</b><br>32<br>33                                                                                                                            |

| Load Quadword (d-form)<br>Load Quadword (x-form)                                                                                                                                                                                                                                                                                                                                                                                                  | <b> 31</b><br>32<br>33<br>34                                                                                                                      |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)                                                                                                                                                                                                                                                                                              | <b> 31</b><br>                                                                                                                                    |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)                                                                                                                                                                                                                                                                   | <b> 31</b><br>                                                                                                                                    |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)                                                                                                                                                                                                             | <b> 31</b><br>32<br>33<br>34<br>34<br>35<br>36<br>36<br>37<br>38                                                                                  |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword (a-form)                                                                                                                                                                                  | <b> 31</b><br>                                                                                                                                    |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword (a-form)<br>Store Quadword (d-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword (a-form)<br>Store Quadword Instruction Relative (a-form)<br>Generate Controls for Byte Insertion (d-form)                                                                                                      | <b> 31</b><br>                                                                                                                                    |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword (a-form)<br>Store Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword (a-form)<br>Generate Controls for Byte Insertion (d-form)<br>Generate Controls for Byte Insertion (x-form)                                                                                | <b> 31</b><br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>39<br>40<br>41                                                                      |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword Instruction Relative (a-form)<br>Generate Controls for Byte Insertion (d-form)<br>Generate Controls for Byte Insertion (x-form)<br>Generate Controls for Byte Insertion (d-form)          | <b> 31</b><br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42                                                                      |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword (a-form)<br>Generate Controls for Byte Insertion (d-form)<br>Generate Controls for Byte Insertion (x-form)<br>Generate Controls for Halfword Insertion (d-form)<br>Generate Controls for Halfword Insertion (x-form) |                                                                                                                                                   |

| Load Quadword (d-form)<br>Load Quadword (x-form)<br>Load Quadword (a-form)<br>Load Quadword Instruction Relative (a-form)<br>Store Quadword (d-form)<br>Store Quadword (x-form)<br>Store Quadword (x-form)<br>Store Quadword (a-form)<br>Store Quadword Instruction Relative (a-form)<br>Generate Controls for Byte Insertion (d-form)<br>Generate Controls for Byte Insertion (x-form)<br>Generate Controls for Byte Insertion (d-form)          | 31         32         33         34         35         36         37         38         39         40         41         42         43         44 |

|        | Generate Controls for Doubleword Insertion (d-form) | 46 |

|--------|-----------------------------------------------------|----|

|        | Generate Controls for Doubleword Insertion (x-form) | 47 |

| 4. Co  | onstant-Formation Instructions                      | 49 |

|        | Immediate Load Halfword                             | 50 |

|        | Immediate Load Halfword Upper                       | 51 |

|        | Immediate Load Word                                 |    |

|        | Immediate Load Address                              | 53 |

|        | Immediate Or Halfword Lower                         |    |

|        | Form Select Mask for Bytes Immediate                | 55 |

| 5. Int | teger and Logical Instructions                      |    |

| -      | Add Halfword                                        |    |

|        | Add Halfword Immediate                              |    |

|        | Add Word                                            |    |

|        | Add Word Immediate                                  |    |

|        | Subtract from Halfword                              |    |

|        | Subtract from Halfword Immediate                    |    |

|        | Subtract from Word                                  |    |

|        | Subtract from Word Immediate                        |    |

|        | Add Extended                                        | 66 |

|        | Carry Generate                                      | 67 |

|        | Carry Generate Extended                             |    |

|        | Subtract from Extended                              | 69 |

|        | Borrow Generate                                     | 70 |

|        | Borrow Generate Extended                            | 71 |

|        | Multiply                                            |    |

|        | Multiply Unsigned                                   | 73 |

|        | Multiply Immediate                                  | 74 |

|        | Multiply Unsigned Immediate                         |    |

|        | Multiply and Add                                    |    |

|        | Multiply High                                       |    |

|        | Multiply and Shift Right                            |    |

|        | Multiply High High                                  | 79 |

|        | Multiply High High and Add                          | 80 |

|        | Multiply High High Unsigned                         |    |

|        | Multiply High High Unsigned and Add                 |    |

|        | Count Leading Zeros                                 |    |

|        | Count Ones in Bytes                                 |    |

|        | Form Select Mask for Bytes                          |    |

|        | Form Select Mask for Halfwords                      |    |

|        | Form Select Mask for Words                          |    |

|        | Gather Bits from Bytes                              |    |

|        | Gather Bits from Halfwords                          |    |

|        | Gather Bits from Words                              |    |

|        | Average Bytes                                       |    |

|        | Absolute Differences of Bytes                       |    |

|        | Sum Bytes into Halfwords                            |    |

|        | Extend Sign Byte to Halfword                        |    |

|        | Extend Sign Halfword to Word                        | 95 |

| And                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| And with Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| And Byte Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| And Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

| And Word Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| Or with Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| Or Byte Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

| Or Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| Or Word Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

| Or Across                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

| Exclusive Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

| Exclusive Or Byte Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| Exclusive Or Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Exclusive Or Word Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| Nand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

| Nor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| Equivalent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

| Select Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| Shuffle Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 116                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| 6. Shift and Rotate Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117                                                                                                                 |

| Shift Left Halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 118                                                                                                                 |

| Shift Left Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 119                                                                                                                 |

| Shift Left Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Shift Left Word Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 121                                                                                                                 |

| Shift Left Quadword by Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 122                                                                                                                 |

| Shift Left Quadword by Bits Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 123                                                                                                                 |

| Shift Left Quadword by Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 124                                                                                                                 |

| Shift Left Quadword by Bytes Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                                                                                 |

| Shift Left Quadword by Bytes from Bit Shift Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126                                                                                                                 |

| Detete Holfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Rotate Halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Rotate Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 128                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Rotate Halfword Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 129                                                                                                                 |

| Rotate Halfword Immediate<br>Rotate Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 129<br>130                                                                                                          |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 129<br>130<br>131                                                                                                   |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 129<br>130<br>131<br>132                                                                                            |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits Immediate<br>Rotate Quadword by Bits Immediate                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits Immediate<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword Immediate                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits Immediate<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword Immediate<br>Rotate and Mask Word                                                                                                                                                                                                                                                                              |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits Immediate<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword Immediate<br>Rotate and Mask Word<br>Rotate and Mask Word                                                                                                                                                                                                                                                      |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits Immediate<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword Immediate<br>Rotate and Mask Word<br>Rotate and Mask Word<br>Rotate and Mask Word Immediate<br>Rotate and Mask Word Immediate |                                                                                                                     |

| Rotate Halfword Immediate<br>Rotate Word<br>Rotate Word Immediate<br>Rotate Quadword by Bytes<br>Rotate Quadword by Bytes Immediate<br>Rotate Quadword by Bytes from Bit Shift Count<br>Rotate Quadword by Bits<br>Rotate Quadword by Bits<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword<br>Rotate and Mask Halfword Immediate<br>Rotate and Mask Word Immediate<br>Rotate and Mask Word Immediate<br>Rotate and Mask Word Immediate<br>Rotate and Mask Word Immediate<br>Rotate and Mask Quadword by Bytes<br>Rotate and Mask Quadword by Bytes Immediate                                                                                   | 129<br>130<br>131<br>132<br>133<br>134<br>134<br>135<br>136<br>137<br>138<br>137<br>138<br>139<br>140<br>141<br>142 |

| Rotate and Mask Algebraic Halfword              | 145 |

|-------------------------------------------------|-----|

| Rotate and Mask Algebraic Halfword Immediate    | 146 |

| Rotate and Mask Algebraic Word                  | 147 |

| Rotate and Mask Algebraic Word Immediate        | 148 |

| -                                               |     |

| 7. Compare, Branch, and Halt Instructions       |     |

| Halt If Equal                                   |     |

| Halt If Equal Immediate                         |     |

| Halt If Greater Than                            |     |

| Halt If Greater Than Immediate                  | 153 |

| Halt If Logically Greater Than                  | 154 |

| Halt If Logically Greater Than Immediate        |     |

| Compare Equal Byte                              |     |

| Compare Equal Byte Immediate                    |     |

| Compare Equal Halfword                          |     |

| Compare Equal Halfword Immediate                |     |

| Compare Equal Word                              |     |

| Compare Equal Word Immediate                    |     |

| Compare Greater Than Byte                       |     |

| Compare Greater Than Byte Immediate             |     |

| Compare Greater Than Halfword                   | 164 |

| Compare Greater Than Halfword Immediate         |     |

| Compare Greater Than Word                       | 166 |

| Compare Greater Than Word Immediate             | 167 |

| Compare Logical Greater Than Byte               |     |

| Compare Logical Greater Than Byte Immediate     | 169 |

| Compare Logical Greater Than Halfword           | 170 |

| Compare Logical Greater Than Halfword Immediate | 171 |

| Compare Logical Greater Than Word               | 172 |

| Compare Logical Greater Than Word Immediate     |     |

| Branch Relative                                 | 174 |

| Branch Absolute                                 | 175 |

| Branch Relative and Set Link                    | 176 |

| Branch Absolute and Set Link                    | 177 |

| Branch Indirect                                 | 178 |

| Interrupt Return                                |     |

| Branch Indirect and Set Link if External Data   | 180 |

| Branch Indirect and Set Link                    | 181 |

| Branch If Not Zero Word                         | 182 |

| Branch If Zero Word                             |     |

| Branch If Not Zero Halfword                     |     |

| Branch If Zero Halfword                         |     |

| Branch Indirect If Zero                         |     |

| Branch Indirect If Not Zero                     |     |

| Branch Indirect If Zero Halfword                |     |

| Branch Indirect If Not Zero Halfword            | 189 |

| 8. | Hint-for-Branch Instructions                                                 | 191   |

|----|------------------------------------------------------------------------------|-------|

|    | Hint for Branch (r-form)                                                     |       |

|    | Hint for Branch (a-form)                                                     |       |

|    | Hint for Branch Relative                                                     |       |

|    |                                                                              |       |

| 9. | Floating-Point Instructions                                                  | 195   |

|    | 9.1 Single Precision (Extended-Range Mode)                                   | . 195 |

|    | 9.2 Double Precision                                                         | . 197 |

|    | 9.2.1 Conversions Between Single-Precision and Double-Precision Format       | . 198 |

|    | 9.2.2 Exception Conditions                                                   | . 198 |

|    | 9.3 Floating-Point Status and Control Register                               | . 200 |

|    | Floating Add                                                                 | . 202 |

|    | Double Floating Add                                                          | . 203 |

|    | Floating Subtract                                                            |       |

|    | Double Floating Subtract                                                     |       |

|    | Floating Multiply                                                            |       |

|    | Double Floating Multiply                                                     |       |

|    | Floating Multiply and Add                                                    |       |

|    | Double Floating Multiply and Add                                             |       |

|    | Floating Negative Multiply and Subtract                                      |       |

|    | Double Floating Negative Multiply and Subtract                               |       |

|    | Floating Multiply and Subtract                                               |       |

|    | Double Floating Multiply and Subtract                                        |       |

|    | Double Floating Negative Multiply and Add                                    |       |

|    | Floating Reciprocal Estimate                                                 |       |

|    | Floating Reciprocal Absolute Square Root Estimate                            |       |

|    | Floating Interpolate                                                         |       |

|    | Convert Signed Integer to Floating                                           |       |

|    | Convert Floating to Signed Integer                                           |       |

|    | Convert Unsigned Integer to Floating<br>Convert Floating to Unsigned Integer |       |

|    | Floating Round Double to Single                                              |       |

|    | Floating Extend Single to Double                                             |       |

|    | Double Floating Compare Equal                                                |       |

|    | Double Floating Compare Agnitude Equal                                       |       |

|    | Double Floating Compare Greater Than                                         |       |

|    | Double Floating Compare Magnitude Greater Than                               |       |

|    | Double Floating Test Special Value                                           |       |

|    | Floating Compare Equal                                                       |       |

|    | Floating Compare Magnitude Equal                                             |       |

|    | Floating Compare Greater Than                                                |       |

|    | Floating Compare Magnitude Greater Than                                      |       |

|    | Floating-Point Status and Control Register Write                             |       |

|    | Floating-Point Status and Control Register Read                              |       |

| 10 | ). Control Instructions                                                      | 237   |

| 10 | Stop and Signal                                                              |       |

|    | Stop and Signal with Dependencies                                            |       |

|    | No Operation (Load)                                                          |       |

|    | $1  \cdots  1  \cdots  1$                                                    |       |

| No Operation (Execute)                                                   | 241 |

|--------------------------------------------------------------------------|-----|

| Synchronize                                                              | 242 |

| Synchronize Data                                                         | 243 |

| Move from Special-Purpose Register                                       | 244 |

| Move to Special-Purpose Register                                         | 245 |

| 11. Channel Instructions                                                 | 247 |

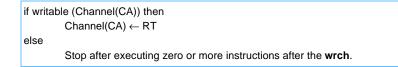

| Read Channel                                                             | 248 |

| Read Channel Count                                                       | 249 |

| Write Channel                                                            | 250 |

| 12. SPU Interrupt Facility                                               | 251 |

| 12.1 SPU Interrupt Handler                                               |     |

| 12.2 SPU Interrupt Facility Channels                                     |     |

| 13. Synchronization and Ordering                                         | 253 |

| 13.1 Speculation, Reordering, and Caching SPU Local Storage Access       |     |

| 13.2 SPU Internal Execution State                                        |     |

| 13.3 Synchronization Primitives                                          |     |

| 13.4 Caching SPU Local Storage Access                                    |     |

| 13.5 Self-Modifying Code                                                 |     |

| 13.6 External Local Storage Access                                       |     |

| 13.7 Speculation and Reordering of Channel Reads and Channel Writes      |     |

| 13.8 Channel Interface with External Device                              |     |

| 13.9 Execution State Set by an SPU Program through the Channel Interface |     |

| 13.10 Execution State Set by an External Device                          |     |

|                                                                          |     |

| Appendix A. Instruction Table Sorted by Instruction Mnemonic             | 259 |

| Appendix B. Details of the Generate Controls Instructions                | 265 |

| Glossary                                                                 | 267 |

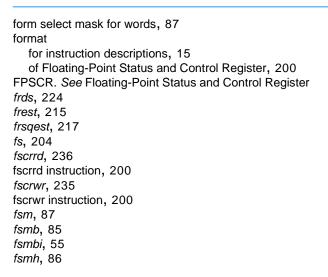

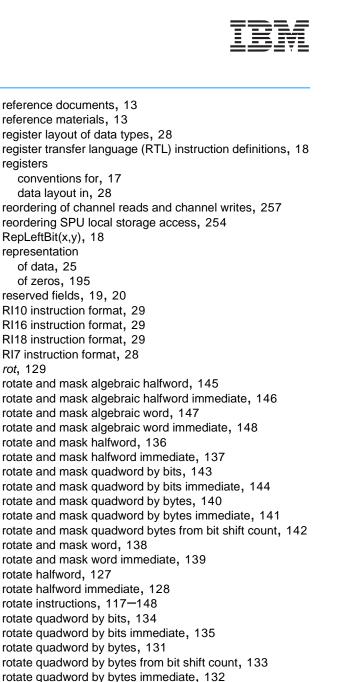

| Index                                                                    | 271 |

# List of Figures

| Figure i.    | Format of an Instruction Description            | 15    |

|--------------|-------------------------------------------------|-------|

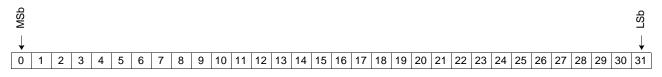

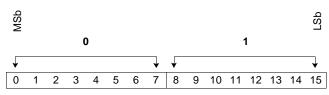

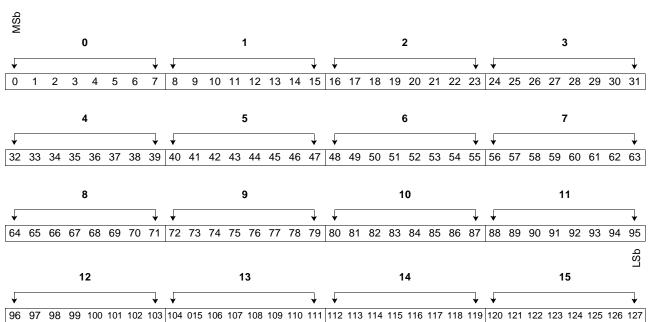

| Figure 2-1.  | Bit and Byte Numbering of Halfwords             | 26    |

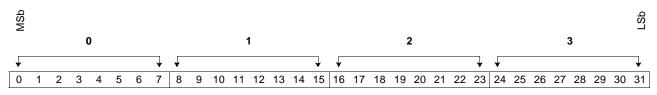

| Figure 2-2.  | Bit and Byte Numbering of Words                 | 26    |

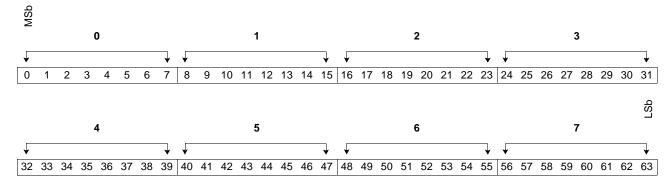

| Figure 2-3.  | Bit and Byte Numbering of Doublewords           | 26    |

| Figure 2-4.  | Bit and Byte Numbering of Quadwords             | 27    |

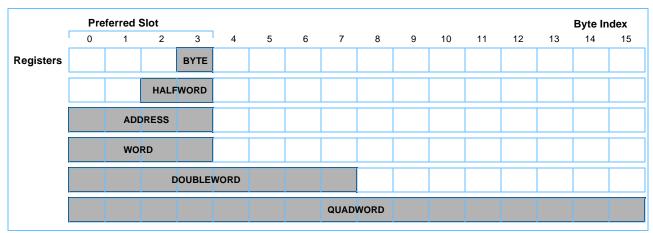

| Figure 2-5.  | Register Layout of Data Types                   | 28    |

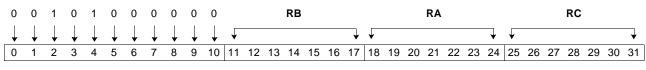

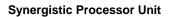

| Figure 2-6.  | RR Instruction Format                           | 28    |

| Figure 2-7.  | RRR Instruction Format                          | 28    |

| Figure 2-8.  | RI7 Instruction Format                          | 28    |

| Figure 2-9.  | RI10 Instruction Format                         | 29    |

| Figure 2-10. | RI16 Instruction Format                         | 29    |

| Figure 2-11. | RI18 Instruction Format                         | 29    |

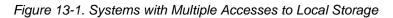

| Figure 13-1. | Systems with Multiple Accesses to Local Storage | . 253 |

## List of Tables

| Table i.    | Temporary Names Used in the RTL and Their Widths                               |     |

|-------------|--------------------------------------------------------------------------------|-----|

| Table ii.   | Instruction Fields                                                             | 19  |

| Table iii.  | Instruction Operation Notations                                                |     |

| Table 1-1.  | Key Features of the SPU ISA Architecture and Implementation                    |     |

| Table 2-1.  | Bit and Byte Numbering Figures                                                 |     |

| Table 3-1.  | Example LSLR Values and Corresponding Local Storage Sizes                      |     |

| Table 5-1.  | Binary Values in Register RC and Byte Results                                  | 116 |

| Table 9-1.  | Single-Precision (Extended-Range Mode) Minimum and Maximum Values              | 195 |

| Table 9-2.  | Instructions and Exception Settings                                            | 196 |

| Table 9-3.  | Double-Precision (IEEE Mode) Minimum and Maximum Values                        | 197 |