## **PowerPC User Instruction Set Architecture**

# **Book I**

## Version 2.02

January 28, 2005

Manager:

Joe Wetzel/Poughkeepsie/IBM

**Technical Content:**

Ed Silha/Austin/IBM Cathy May/Watson/IBM Brad Frey/Austin/IBM

Junichi Furukawa/Austin/IBM Giles Frazier/Austin/IBM

The following paragraph does not apply to the United Kingdom or any country or state where such provisions are inconsistent with local law.

The specifications in this manual are subject to change without notice. This manual is provided "AS IS". International Business Machines Corp. makes no warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

International Business Machines Corp. does not warrant that the contents of this publication or the accompanying source code examples, whether individually or as one or more groups, will meet your requirements or that the publication or the accompanying source code examples are error-free.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication.

Address comments to IBM Corporation, Internal Zip 9630, 11400 Burnett Road, Austin, Texas 78758-3493. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

The following terms are trademarks of the International Business Machines Corporation in the United States and/or other countries:

IBM PowerPC RISC/System 6000 POWER POWER2 POWER4 POWER4+ IBM System/370

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set fourth in GSA ADP Schedule Contract with IBM Corporation.

© Copyright International Business Machines Corporation, 1994, 2003. All rights reserved.

## **Preface**

This document defines the PowerPC User Instruction Set Architecture. It covers the base instruction set and related facilities available to the application program-

Other related documents define the PowerPC Virtual Environment Architecture, the PowerPC Operating Environment Architecture, and PowerPC Implementation Features. Book II, PowerPC Virtual Environment Architecture defines the storage model and related instructions and facilities available to the application programmer, and the time-keeping facilities available to the application programmer. Book III, PowerPC Operating Environment Architecture defines the system (privileged) instructions and related facilities. Book IV, PowerPC Implementation Features defines the implementation-dependent aspects of a particular implementation.

As used in this document, the term "PowerPC Architecture" refers to the instructions and facilities described in Books I. II. and III. The description of the instantiation of the PowerPC Architecture in a given implementation includes also the material in Book IV for that implementation.

Note: Change bars indicate changes from Version 2.01.

# **Table of Contents**

| Chapter 1. Introduction 1                    | 2.3.1 Condition Register 18                                                          |

|----------------------------------------------|--------------------------------------------------------------------------------------|

| 1.1 Overview 1                               | 2.3.2 Link Register 19                                                               |

| 1.2 Computation modes 1                      | 2.3.3 Count Register                                                                 |

| 1.3 Instruction Mnemonics and Operands1      | 2.4 Branch Processor Instructions 20                                                 |

| 1.4 Compatibility with the POWER Archi-      | 2.4.1 Branch Instructions 20                                                         |

| tecture2                                     | 2.4.2 System Call Instruction 26                                                     |

| 1.5 Document Conventions 2                   | 2.4.3 Condition Register Logical Instruc-                                            |

| 1.5.1 Definitions and Notation 2             | tions                                                                                |

| 1.5.2 Reserved Fields and Reserved Val-      | 2.4.4 Condition Register Field                                                       |

| ues                                          | Instruction                                                                          |

| 1.5.3 Description of Instruction Operation 4 |                                                                                      |

| 1.6 Processor Overview 6                     | Chapter 3. Fixed-Point Processor .31                                                 |

| 1.7 Instruction formats                      | 3.1 Fixed-Point Processor Overview31                                                 |

| 1.7.1 I-Form                                 | 3.2 Fixed-Point Processor                                                            |

| 1.7.2 B-Form                                 |                                                                                      |

| 1.7.2 B-F0111 8                              | Registers                                                                            |

|                                              | 3.2.1 General Purpose Registers 31                                                   |

|                                              | 3.2.2 Fixed-Point Exception Register 32                                              |

| 1.7.5 DS-FORM                                | 3.3 Fixed-Point Processor Instructions . 33                                          |

| 1.7.6 X-FORM                                 | 3.3.1 Fixed-Point Storage Access Instruc-                                            |

| 1.7.7 XL-FORM                                | tions                                                                                |

| 1.7.8 XFX-FORM                               | 3.3.1.1 Storage Access Exceptions 33                                                 |

| 1.7.9 XFL-FORM 9                             | 3.3.2 Fixed-Point Load Instructions 33                                               |

| 1.7.10 XS-FORM 9                             | 3.3.3 Fixed-Point Store Instructions 40                                              |

| 1.7.11 XO-FORM 9                             | 3.3.4 Fixed-Point Load and Store with Byte                                           |

| 1.7.12 A-FORM                                | Reversal Instructions 44                                                             |

| 1.7.13 M-FORM 10                             | 3.3.5 Fixed-Point Load and Store Multiple                                            |

| 1.7.14 MD-FORM                               | Instructions 46                                                                      |

| 1.7.15 MDS-FORM                              | 3.3.6 Fixed-Point Move Assist Instruc-                                               |

| 1.7.16 Instruction Fields 10                 | tions47                                                                              |

| 1.8 Classes of Instructions 12               | 3.3.7 Other Fixed-Point Instructions 50                                              |

| 1.8.1 Defined Instruction Class 12           | 3.3.8 Fixed-Point Arithmetic Instructions 51                                         |

| 1.8.2 Illegal Instruction Class 12           | 3.3.9 Fixed-Point Compare Instructions 60                                            |

| 1.8.3 Reserved Instruction Class 12          | 3.3.10 Fixed-Point Trap Instructions 62                                              |

| 1.9 Forms of Defined Instructions 13         | 3.3.11 Fixed-Point Logical Instructions . 65                                         |

| 1.9.1 Preferred Instruction Forms 13         | 3.3.12 Fixed-Point Rotate and Shift                                                  |

| 1.9.2 Invalid Instruction Forms 13           | Instructions71                                                                       |

| 1.10 Optionality14                           | 3.3.12.1 Fixed-Point Rotate Instructions 71                                          |

| 1.11 Exceptions                              | 3.3.12.2 Fixed-Point Shift Instructions . 77                                         |

| 1.12 Storage Addressing 14                   | 3.3.13 Move To/From System Register                                                  |

| 1.12.1 Storage Operands 14                   | Instructions 81                                                                      |

| 1.12.2 Effective Address Calculation 15      |                                                                                      |

|                                              | Chapter 4. Floating-Point Processor.                                                 |

| Chapter 2. Branch Processor 17               | 85                                                                                   |

| 2.1 Branch Processor Overview 17             | 4.1 Floating-Point Processor Overview. 85                                            |

| 2.2 Instruction Execution Order 17           | 4.1 Floating-Point Processor Overview. 85 4.2 Floating-Point Processor Registers. 86 |

| 2.3 Branch Processor Registers 18            | 7.2 I loating-rount Flocessor Negisters. 00                                          |

| · · · · · · · · · · · · · · · · · · ·        |                                                                                      |

| 4.2.1 Floating-Point Registers 86            | Chapter 5. Optional Facilities and           |

|----------------------------------------------|----------------------------------------------|

| 4.2.2 Floating-Point Status and Control      | Instructions 123                             |

| Register                                     | 5.1 Fixed-Point Processor Instructions 124   |

| 4.3 Floating-Point Data                      | 5.1.1 Move To/From System Register           |

| 4.3.1 Data Format                            | Instructions                                 |

| 4.3.2 Value Representation                   | 5.2 Floating-Point Processor Instructions.   |

| 4.3.3 Sign of Result                         | 124                                          |

| 4.3.4 Normalization and                      | 5.2.1 Floating-Point Arithmetic Instructions |

| Denormalization                              | 125                                          |

| 4.3.5 Data Handling and Precision 92         | 5.2.1.1 Floating-Point Elementary Arith-     |

| 4.3.5.1 Single-Precision Operands 92         | metic Instructions                           |

| 4.3.5.2 Integer-Valued Operands 93           | 5.2.2 Floating-Point Select Instruction 126  |

| 4.3.6 Rounding                               | 5.3 Little-Endian                            |

| 4.4 Floating-Point Exceptions 94             | 5.3.1 Byte Ordering                          |

| 4.4.1 Invalid Operation Exception 96         | 5.3.2 Structure Mapping Examples 127         |

| 4.4.1.1 Definition                           | 5.3.2.1 Big-Endian Mapping 127               |

| 4.4.1.2 Action                               | 5.3.2.2 Little-Endian Mapping 128            |

| 4.4.2 Zero Divide Exception97                | 5.3.3 PowerPC Byte Ordering 128              |

| 4.4.2.1 Definition                           | 5.3.3.1 Controlling PowerPC Byte Order-      |

| 4.4.2.2 Action                               | ing128                                       |

| 4.4.3 Overflow Exception                     | 5.3.3.2 PowerPC Little-Endian Byte Order-    |

| 4.4.3.1 Definition                           | ing                                          |

| 4.4.3.2 Action                               | 5.3.4 PowerPC Data Addressing in Little-     |

| 4.4.4 Underflow Exception                    | Endian Mode                                  |

| 4.4.4.1 Definition                           | 5.3.4.1 Individual Aligned Scalars 130       |

| 4.4.4.2 Action                               | 5.3.4.2 Other Scalars                        |

| 4.4.5 Inexact Exception                      | 5.3.4.3 Page Table                           |

| 4.4.5.1 Definition                           | 5.3.5 PowerPC Instruction Addressing in      |

| 4.4.5.2 Action                               | Little-Endian Mode                           |

| 4.5 Floating-Point Execution Models100       | 5.3.6 PowerPC Cache                          |

| 4.5.1 Execution Model for IEEE Opera-        | Management Instructions in                   |

| tions                                        | Little-Endian Mode                           |

| 4.5.2 Execution Model for                    | 5.3.7 PowerPC I/O in                         |

| Multiply-Add Type Instructions 101           | Little-Endian Mode                           |

| 4.6 Floating-Point Processor Instructions .  | 5.3.8 Origin of Endian                       |

| 103                                          | 0.0.0 Origin of Endian.                      |

| 4.6.1 Floating-Point Storage Access          | Chapter 6. Optional Facilities and           |

| Instructions                                 |                                              |

| 4.6.1.1 Storage Access Exceptions 103        | Instructions that are being Phased           |

| 4.6.2 Floating-Point Load Instructions .103  | Out                                          |

| 4.6.3 Floating-Point Store Instructions .106 | 6.1 Move To Condition Register from          |

| 4.6.4 Floating-Point Move Instructions . 110 | XER 135                                      |

| 4.6.5 Floating-Point Arithmetic Instructions |                                              |

| 111                                          | Appendix A. Suggested Floating-              |

| 4.6.5.1 Floating-Point Elementary Arith-     | Point Models                                 |

| metic Instructions                           |                                              |

| 4.6.5.2 Floating-Point Multiply-Add Instruc- | A.1 Floating-Point Round to Single-Preci-    |

| tions                                        | sion Model                                   |

| 4.6.6 Floating-Point Rounding and Con-       | A.2 Floating-Point Convert to Integer        |

| version Instructions                         | Model                                        |

| 4.6.7 Floating-Point Compare Instructions.   | A.3 Floating-Point Convert from Integer      |

| 119                                          | Model                                        |

| 4.6.8 Floating-Point Status and Control      |                                              |

| Register Instructions120                     | Appendix B. Assembler Extended               |

|                                              | Mnemonics 151                                |

|                                              | B.1 Symbols                                  |

|                                              | D.1 Ojiilolo                                 |

| B.2 Branch Mnemonics 152                                                            | C.3.3 Simple if-then-else                                                              |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| B.2.1 BO and BI Fields 152                                                          | Constructions                                                                          |

| B.2.2 Simple Branch Mnemonics 152                                                   | C.3.4 Notes                                                                            |

| B.2.3 Branch Mnemonics Incorporating                                                | Annon din D. Onco Defendance for                                                       |

| Conditions                                                                          | Appendix D. Cross-Reference for                                                        |

| B.3 Condition Register Logical Mnemonics                                            | Changed POWER Mnemonics173                                                             |

| 155                                                                                 |                                                                                        |

| B.4 Subtract Mnemonics 155                                                          | Appendix E. Incompatibilities with                                                     |

| B.4.1 Subtract Immediate 155                                                        | the POWER Architecture175                                                              |

| B.4.2 Subtract                                                                      | E.1 New Instructions, Formerly Privileged                                              |

| B.5 Compare Mnemonics 156                                                           | Instructions                                                                           |

| B.5.1 Doubleword Comparisons 157                                                    | E.2 Newly Privileged                                                                   |

| B.5.2 Word Comparisons                                                              | Instructions                                                                           |

| B.6 Trap Mnemonics                                                                  | E.3 Reserved Fields in                                                                 |

| B.7.1 Operations on Doublewords 159                                                 | Instructions                                                                           |

| B.7.2 Operations on Words 160                                                       | E.4 Reserved Bits in Registers 175 E.5 Alignment Check 175                             |

| B.8 Move To/From Special Purpose Regis-                                             | E.5 Alignment Check                                                                    |

| ter Mnemonics                                                                       | E.7 LK and Rc Bits 176                                                                 |

| B.9 Miscellaneous Mnemonics 162                                                     | E.8 BO Field                                                                           |

|                                                                                     | E.9 BH Field                                                                           |

| Appendix C. Programming Examples                                                    | E.10 Branch Conditional to Count Register                                              |

| 167                                                                                 | 176                                                                                    |

| C.1 Multiple-Precision Shifts 167                                                   | E.11 System Call176                                                                    |

| C.2 Floating-Point Conversions 170                                                  | E.12 Fixed-Point Exception                                                             |

| C.2.1 Conversion from                                                               | Register (XER) 177                                                                     |

| Floating-Point Number to                                                            | E.13 Update Forms of Storage Access                                                    |

| Floating-Point Integer 170                                                          | Instructions                                                                           |

| C.2.2 Conversion from                                                               | E.14 Multiple Register Loads 177 E.15 Load/Store Multiple Instructions . 177           |

| Floating-Point Number to Signed Fixed-                                              | E.16 Move Assist Instructions 178                                                      |

| Point Integer Doubleword 170                                                        | E.17 Move To/From SPR 178                                                              |

| C.2.3 Conversion from                                                               | E.18 Effects of Exceptions on FPSCR Bits                                               |

| Floating-Point Number to Unsigned Fixed-<br>Point Integer Doubleword 170            | FR and FI                                                                              |

| C.2.4 Conversion from                                                               | E.19 Store Floating-Point Single Instruc-                                              |

| Floating-Point Number to Signed Fixed-                                              | tions                                                                                  |

| Point Integer Word                                                                  | E.20 Move From FPSCR                                                                   |

| C.2.5 Conversion from                                                               | E.21 Zeroing Bytes in the Data Cache 178                                               |

| Floating-Point Number to Unsigned Fixed-                                            | <ul><li>E.22 Synchronization 179</li><li>E.23 Move To Machine State Register</li></ul> |

| Point Integer Word                                                                  | Instruction                                                                            |

| C.2.6 Conversion from Signed Fixed-Point                                            | E.24 Direct-Store Segments 179                                                         |

| Integer Doubleword to Floating-Point Num-                                           | E.25 Segment Register                                                                  |

| ber                                                                                 | Manipulation Instructions                                                              |

| C.2.7 Conversion from Unsigned Fixed-<br>Point Integer Doubleword to Floating-Point | E.26 TLB Entry Invalidation 179                                                        |

| Number                                                                              | E.27 Alignment Interrupts 179                                                          |

| C.2.8 Conversion from Signed Fixed-Point                                            | E.28 Floating-Point Interrupts 179                                                     |

| Integer Word to Floating-Point Number 171                                           | E.29 Timing Facilities                                                                 |

| C.2.9 Conversion from Unsigned Fixed-                                               | E.29.1 Real-Time Clock                                                                 |

| Point Integer Word to Floating-Point Num-                                           | E.29.2 Decrementer                                                                     |

| ber 171                                                                             | E.30 Deleted Instructions                                                              |

| C.3 Floating-Point Selection 172                                                    | E.31 Discontinued Opcodes 181 E.32 POWER2 Compatibility 181                            |

| C.3.1 Comparison to Zero 172                                                        | E.32.1 Cross-Reference for Changed                                                     |

| C.3.2 Minimum and Maximum 172                                                       | POWER2 Mnemonics                                                                       |

|                                                                                     | . 3                                                                                    |

| E.32.2                      | Floating-Point Conversion to Inte- |

|-----------------------------|------------------------------------|

| E.32.3 F<br>E.32.4 E.32.5 F |                                    |

| Appendix F                  | . New Instructions 185             |

| Appendix G                  | 6. Illegal Instructions . 187      |

| Appendix H<br>189           | I. Reserved Instructions .         |

| Appendix I.                 | Opcode Maps191                     |

| • •                         | PowerPC Instruction Set Opcode 203 |

| Appendix K                  | . PowerPC Instruction              |

# **Figures**

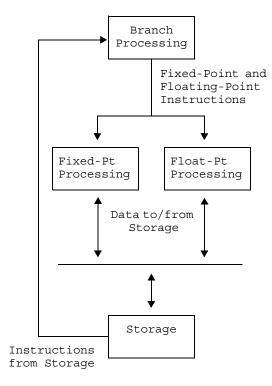

| 1.   | Logical processing mode                 | . 6  |

|------|-----------------------------------------|------|

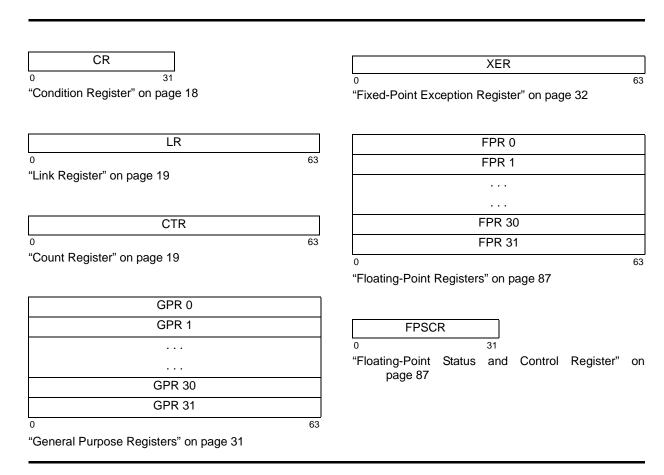

| 2.   | Power PC user register set              |      |

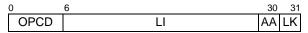

| 3.   | I instruction format                    |      |

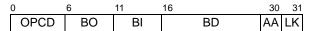

| 4.   | B instruction format                    |      |

| 5.   | SC instruction format                   | . 8  |

| 6.   | D instruction format                    | . 8  |

| 7.   | DS instruction format                   |      |

| 8.   | X instruction format                    |      |

| 9.   | XL instruction format                   |      |

| 10.  |                                         |      |

| 11.  |                                         |      |

| 12.  |                                         |      |

| 13.  |                                         |      |

| 14.  |                                         | 10   |

| 15.  |                                         | 10   |

| 16.  |                                         | 10   |

| 17.  |                                         | 10   |

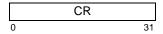

| 18.  |                                         | 18   |

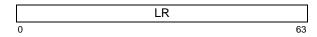

| 19.  |                                         | 19   |

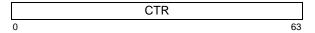

| 20.  |                                         | 19   |

| 21.  |                                         | 20   |

| 22.  | <u> </u>                                | 20   |

| 23.  |                                         | 21   |

| 24.  |                                         | 31   |

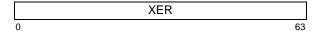

| 25.  |                                         | 32   |

| 26.  | · · · · · · · · · · · · · · · · · · ·   | 65   |

| 27.  | -                                       | 87   |

| 28.  |                                         | 87   |

| 29.  |                                         | 89   |

| 30.  | 3                                       | 90   |

| 31.  | · · · · · · · · · · · · · · · · · · ·   | 90   |

| 32.  |                                         | 90   |

| 33.  | ~ .                                     | 90   |

| 34.  |                                         | 94   |

| 35.  |                                         | 100  |

| 36.  |                                         | 100  |

| 37.  | •                                       |      |

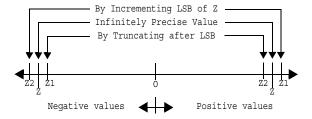

| · .  | Sticky bits in the IEEE execution model | 101  |

| 38.  |                                         | 101  |

| 39.  |                                         |      |

|      | multiply-add execution model            | 102  |

| 40.  |                                         | 128  |

| 41.  | •                                       | 128  |

| 42.  |                                         | 128  |

| 43.  | · · · ·                                 | .20  |

| .0.  | in storage subsystem                    | 129  |

| 44.  |                                         | . 20 |

| . 7. | as seen by processor                    | 130  |

|      | ac ccc by procedure                     | . 00 |

| 15.             | Little-Englan mapping of word 'w'          |     |

|-----------------|--------------------------------------------|-----|

|                 | stored at address 5                        | 131 |

| <del>1</del> 6. | PowerPC Little-Endian, word 'w'            |     |

|                 | stored at address 5 in storage subsystem . | 131 |

| <del>1</del> 7. | Assembly language program 'p'              | 131 |

| <del>1</del> 8. | Big-Endian mapping of program 'p'          | 132 |

| <del>1</del> 9. | Little-Endian mapping of program 'p'       | 132 |

| 50.             | PowerPC Little-Endian, program 'p'         |     |

|                 | in storage subsystem                       | 132 |

## **Chapter 1. Introduction**

| 1.1 Overview                                 | 1.7.10 XS-FORM9                         |

|----------------------------------------------|-----------------------------------------|

| 1.2 Computation modes 1                      | 1.7.11 XO-FORM9                         |

| 1.3 Instruction Mnemonics and Operands1      | 1.7.12 A-FORM                           |

| 1.4 Compatibility with the POWER Archi-      | 1.7.13 M-FORM                           |

| tecture                                      | 1.7.14 MD-FORM                          |

| 1.5 Document Conventions 2                   | 1.7.15 MDS-FORM                         |

| 1.5.1 Definitions and Notation 2             | 1.7.16 Instruction Fields               |

| 1.5.2 Reserved Fields and Reserved Val-      | 1.8 Classes of Instructions             |

| ues                                          | 1.8.1 Defined Instruction Class 12      |

| 1.5.3 Description of Instruction Operation 4 | 1.8.2 Illegal Instruction Class 12      |

| 1.6 Processor Overview 6                     | 1.8.3 Reserved Instruction Class 12     |

| 1.7 Instruction formats 7                    | 1.9 Forms of Defined Instructions 13    |

| 1.7.1 I-Form 8                               | 1.9.1 Preferred Instruction Forms 13    |

| 1.7.2 B-Form 8                               | 1.9.2 Invalid Instruction Forms 13      |

| 1.7.3 SC-Form 8                              | 1.10 Optionality                        |

| 1.7.4 D-Form 8                               | 1.11 Exceptions                         |

| 1.7.5 DS-FORM 8                              | 1.12 Storage Addressing                 |

| 1.7.6 X-FORM 9                               | 1.12.1 Storage Operands 14              |

| 1.7.7 XL-FORM 9                              | 1.12.2 Effective Address Calculation 15 |

| 1.7.8 XFX-FORM 9                             |                                         |

| 1.7.9 XFL-FORM 9                             |                                         |

|                                              |                                         |

## 1.1 Overview

This chapter describes computation modes, compatibility with the POWER Architecture, document conventions, a processor overview, instruction formats, storage addressing, and instruction fetching.

## 1.2 Computation modes

Processors provide two execution environments, 32-bit and 64-bit. In both of these environments (modes), instructions that set a 64-bit register affect all 64 bits, and the value placed into the register is independent of mode.

# 1.3 Instruction Mnemonics and Operands

The description of each instruction includes the mnemonic and a formatted list of operands. Some examples are the following.

stw RS,D(RA) addis RT,RA,SI

PowerPC-compliant Assemblers will support the mnemonics and operand lists exactly as shown. They should also provide certain extended mnemonics, as described in Appendix B, "Assembler Extended Mnemonics" on page 151.

# 1.4 Compatibility with the POWER Architecture

The PowerPC Architecture provides binary compatibility for POWER application programs, except as described in Appendix E, "Incompatibilities with the POWER Architecture" on page 175.

Many of the PowerPC instructions are identical to POWER instructions. For some of these the PowerPC instruction name and/or mnemonic differs from that in POWER. To assist readers familiar with the POWER Architecture, POWER mnemonics are shown with the individual instruction descriptions when they differ from the PowerPC mnemonics. Also, Appendix D, "Cross-Reference for Changed POWER Mnemonics" on page 173 provides a cross-reference from POWER mnemonics to PowerPC mnemonics for the instructions in Books I, II, and III.

References to the POWER Architecture include POWER2 implementations of the POWER Architecture unless otherwise stated.

## 1.5 Document Conventions

#### 1.5.1 Definitions and Notation

The following definitions and notation are used throughout the PowerPC Architecture documents.

- A program is a sequence of related instructions.

- An application program is a program that uses only the instructions and resources described in Books I and II.

- Quadwords are 128 bits, doublewords are 64 bits, words are 32 bits, halfwords are 16 bits, and bytes are 8 bits.

- All numbers are decimal unless specified in some special way.

- Obnnnn means a number expressed in binary format.

- 0xnnnn means a number expressed in hexadecimal format.

Underscores may be used between digits.

- RT, RA, R1, ... refer to General Purpose Registers.

- FRT, FRA, FR1, ... refer to Floating-Point Registers.

- (x) means the contents of register x, where x is the name of an instruction field. For example, (RA) means the contents of register RA, and (FRA) means the contents of register FRA, where RA and FRA are instruction fields. Names such as LR and CTR denote registers, not fields, so parentheses

- are not used with them. Parentheses are also omitted when register x is the register into which the result of an operation is placed.

- (RA|0) means the contents of register RA if the RA field has the value 1-31, or the value 0 if the RA field is 0.

- Bits in registers, instructions, and fields are specified as follows.

- Bits are numbered left to right, starting with bit

- Ranges of bits are specified by two numbers separated by a colon (:). The range p:q consists of bits p through q.

- X<sub>p</sub> means bit p of register/field X.

- X<sub>p:q</sub> means bits p through q of register/field X.

- $X_{p q \dots}$  means bits p, q, ... of register/field X.

- ¬(RA) means the one's complement of the contents of register RA.

- Field i refers to bits 4×i through 4×i+3 of a register.

- A period (.) as the last character of an instruction mnemonic means that the instruction records status information in certain fields of the Condition Register as a side effect of execution, as described in Chapter 2 through Chapter 4.

- The symbol || is used to describe the concatenation of two values. For example, 010 || 111 is the same as 010111.

- x<sup>n</sup> means x raised to the n<sup>th</sup> power.

- nx means the replication of x, n times (i.e., x concatenated to itself n-1 times). (n)0 and (n)1 are special cases:

- no means a field of n bits with each bit equal to

Thus 50 is equivalent to 0b00000.

- n1 means a field of n bits with each bit equal to

1. Thus 51 is equivalent to 0b111111.

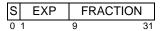

- Floating-point single format or simply single format is used to refer to the representation of a single-precision binary floating-point value in a register or storage.

- Floating-point double format or simply double format is used to refer to the representation of a double-precision binary floating-point value in a register or storage.

- Positive means greater than zero.

- Negative means less than zero.

- A system library program is a component of the system software that can be called by an application program using a *Branch* instruction.

- A system service program is a component of the system software that can be called by an application program using a System Call instruction.

- The system trap handler is a component of the system software that receives control when the conditions specified in a *Trap* instruction are satisfied.

- The system error handler is a component of the system software that receives control when an error occurs. The system error handler includes a component for each of the various kinds of error. These error-specific components are referred to as the system alignment error handler, the system data storage error handler, etc.

- Each bit and field in instructions, and in status and control registers (e.g., XER, FPSCR) and Special Purpose Registers, is either defined or reserved.

- /, //, ///, ... denotes a reserved field in an instruction.

- Latency refers to the interval from the time an instruction begins execution until it produces a result that is available for use by a subsequent instruction.

- Unavailable refers to a resource that cannot be used by the program. For example, storage is unavailable if access to it is denied. See Book III, PowerPC Operating Environment Architecture.

- A value that is specified as being undefined may vary between implementations, and between different executions on the same implementation, and similarly for register contents, storage contents, etc., that are specified as being undefined.

- The results of executing a given instruction are said to be boundedly undefined if they could have been achieved by executing an arbitrary finite sequence of instructions (none of which yields boundedly undefined results) in the state the processor was in before executing the given instruction. Boundedly undefined results may include the presentation of inconsistent state to the system error handler as described in the section entitled "Concurrent Modification and Execution of Instructions" in Book II. Boundedly undefined results for a given instruction may vary between implementations, and between different executions on the same implementation.

- The sequential execution model is the model of program execution described in Section 2.2, "Instruction Execution Order" on page 17.

# 1.5.2 Reserved Fields and Reserved Values

Reserved fields in instructions are ignored by the processor.

In some cases a defined field of an instruction has certain values that are reserved. This includes cases in which the field is shown in the instruction layout as containing a particular value; in such cases all other values of the field are reserved. In general, if an instruction is coded such that a defined field contains a reserved value the instruction form is invalid; see Section 1.9.2 on page 13. The only exception to the preceding rule is that it does not apply to portions of defined fields that are specified, in the instruction description, as being treated as a reserved field. References elsewhere in Books I - III to a defined field that has reserved values assume the field does not contain a reserved value, unless otherwise stated or obvious from context.

To maximize compatibility with future architecture extensions, software must ensure that reserved fields in instructions contain zero and that defined fields of instructions do not contain reserved values.

The handling of reserved bits in System Registers (e.g., XER, FPSCR) is implementation-dependent. Unless otherwise stated, software is permitted to write any value to such a bit. A subsequent reading of the bit returns 0 if the value last written to the bit was 0 and returns an undefined value (0 or 1) otherwise.

#### Assembler Note

Assemblers should report uses of reserved values of defined fields of instructions as errors.

#### Programming Note

It is the responsibility of software to preserve bits that are now reserved in System Registers, because they may be assigned a meaning in some future version of the architecture.

In order to accomplish this preservation in implementation-independent fashion, software should do the following.

- Initialize each such register supplying zeros for all reserved bits.

- Alter (defined) bit(s) in the register by reading the register, altering only the desired bit(s), and then writing the new value back to the register.

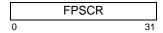

The XER and FPSCR are partial exceptions to this recommendation. Software can alter the status bits in these registers, preserving the reserved bits, by executing instructions that have the side effect of altering the status bits. Similarly, software can alter any defined bit in the FPSCR by executing a Floating-Point Status and Control Register instruction. Using such instructions is likely to yield better performance than using the method described in the second item above.

# 1.5.3 Description of Instruction Operation

A formal description is given of the operation of each instruction. In addition, the operation of most instructions is described by a semiformal language at the register transfer level (RTL). This RTL uses the notation given below, in addition to the definitions and notation described in Section 1.5.1, "Definitions and Notation" on page 2. Some of this notation is also used in the formal descriptions of instructions. RTL notation not summarized here should be self-explanatory.

The RTL descriptions cover the normal execution of the instruction, except that "standard" setting of the Condition Register, Fixed-Point Exception Register, and Floating-Point Status and Control Register are not shown. ("Non-standard" setting of these registers, such as the setting of the Condition Register by the *Compare* instructions, is shown.) The RTL descriptions do not cover cases in which the system error handler is invoked, or for which the results are boundedly undefined.

The RTL descriptions specify the architectural transformation performed by the execution of an instruction. They do not imply any particular implementation.

### Notation Meaning

|                        | A:                                                             |

|------------------------|----------------------------------------------------------------|

| ←                      | Assignment                                                     |

| ←iea                   | Assignment of an instruction effective                         |

|                        | address. In 32-bit mode the high-order 32                      |

|                        | bits of the 64-bit target address are set to                   |

|                        | 0.                                                             |

| ¬                      | NOT logical operator                                           |

| +                      | Two's complement addition                                      |

| -                      | Two's complement subtraction, unary                            |

|                        | minus                                                          |

| ×                      | Multiplication                                                 |

| ÷                      | Division (yielding quotient)                                   |

| $\sqrt{}$              | Square root                                                    |

| <b>=</b> , ≠           | Equals, Not Equals relations                                   |

| <, ≤, >, ≥             | Signed comparison relations                                    |

| <u,>u, =, -, =</u,>    | Unsigned comparison relations                                  |

| ?                      | Unordered comparison relation                                  |

| &,                     | AND, OR logical operators                                      |

| ⊕, ≡                   | Exclusive OR, Equivalence logical opera-                       |

| Ψ, –                   | tors $((a \equiv b) = (a \oplus \neg b))$                      |

| ABS(x)                 | Absolute value of x                                            |

| CEIL(x)                | Least integer ≥ x                                              |

|                        |                                                                |

| DOODLE(X               | Result of converting x from floating-point                     |

|                        | single format to floating-point double for-                    |

| EVTO()                 | mat, using the model shown on page 103                         |

| EXTS(x)                | Result of extending x on the left with sign                    |

|                        | bits                                                           |

| FLOOR(x)               |                                                                |

| GPR(x)                 | General Purpose Register x                                     |

| MASK(x, y)             | Mask having 1s in positions x through y                        |

|                        | (wrapping if $x > y$ ) and 0s elsewhere                        |

| MEM(x, y)              | Contents of y bytes of storage starting at                     |

|                        | address x. In 32-bit mode the high-order                       |

|                        | 32 bits of the 64-bit value x are ignored.                     |

| $ROTL_{64}(x, y)$      | y)                                                             |

|                        | Result of rotating the 64-bit value x left y                   |

|                        | positions                                                      |

| ROTL <sub>32</sub> (x, | •                                                              |

| 32( 7 )                | Result of rotating the 64-bit value x  x left y                |

|                        | positions, where x is 32 bits long                             |

| SINGLE(x)              | Result of converting x from floating-point                     |

| (N)                    | double format to floating-point single for-                    |

|                        | mat, using the model shown on page 106                         |

| SPREG(x)               | Special Purpose Register x                                     |

| TRAP                   | Invoke the system trap handler                                 |

| characteriza           | ·                                                              |

| CilaiaCleilZ           | Reference to the setting of status bits, in a                  |

|                        |                                                                |

| المطمئة عا             | standard way that is explained in the text An undefined value. |

| undefined              |                                                                |

| CIA                    | Current Instruction Address, which is the                      |

|                        | 64-bit address of the instruction being                        |

|                        | described by a sequence of RTL. Used by                        |

|                        | relative branches to set the Next Instruc-                     |

|                        | tion Address (NIA), and by Branch instruc-                     |

|                        | tions with LK=1 to set the Link Register. In                   |

|                        | 32-bit mode the high-order 32 bits of CIA                      |

|                        | are always set to 0. Does not correspond                       |

|                        | to any architected register                                    |

to any architected register.

Next Instruction Address, which is the 64-bit address of the next instruction to be

executed. For a successful branch, the

NIA

next instruction address is the branch target address: in RTL, this is indicated by assigning a value to NIA. For other instructions that cause non-sequential instruction fetching (see Book III, PowerPC Operating Environment Architecture), the RTL is similar. For instructions that do not branch, and do not otherwise cause instruction fetching non-sequential, the next instruction address is CIA+4. In 32-bit mode the high-order 32 bits of NIA are always set to 0. Does not correspond to any architected register.

if... then... else...

Conditional execution, indenting shows

range; else is optional.

Do loop, indenting shows range. "To" and/ do or "by" clauses specify incrementing an iteration variable, and a "while" clause

gives termination conditions.

leave Leave innermost do loop, or do loop

described in leave statement.

for For loop, indenting shows range. Clause

after "for" specifies the entities for which to

execute the body of the loop.

The precedence rules for RTL operators are summarized in Table 1. Operators higher in the table are applied before those lower in the table. Operators at the same level in the table associate from left to right, from right to left, or not at all, as shown. (For example, - associates from left to right, so a-b-c = (a-b)-c.) Parentheses are used to override the evaluation order implied by the table or to increase clarity; parenthesized expressions are evaluated before serving as operands.

| Table 1: Operator precedence                                                         |               |

|--------------------------------------------------------------------------------------|---------------|

| Operators                                                                            | Associativity |

| subscript, function evaluation                                                       | left to right |

| pre-superscript (replication), post-superscript (exponentiation)                     | right to left |

| unary -, ¬                                                                           | right to left |

| ×, ÷                                                                                 | left to right |

| +, -,                                                                                | left to right |

|                                                                                      | left to right |

| $=$ , $\neq$ , $<$ , $\leq$ , $>$ , $\geq$ , $<$ <sup>u</sup> , $>$ <sup>u</sup> , ? | left to right |

| &, ⊕, ≡                                                                              | left to right |

|                                                                                      | left to right |

| : (range)                                                                            | none          |

| ←                                                                                    | none          |

### 1.6 Processor Overview

The processor implements the instruction set, the storage model, and other facilities defined in this document. Instructions that the processor can execute fall into three classes:

- branch instructions

- fixed-point instructions

- floating-point instructions

Branch instructions are described in Section 2.4, "Branch Processor Instructions" on page 20. Fixed-point instructions are described in Section 3.3, "Fixed-Point Processor Instructions" on page 33. Floating-point instructions are described in Section 4.6, "Floating-Point Processor Instructions" on page 103.

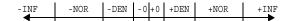

Fixed-point instructions operate on byte, halfword, word, and doubleword operands. Floating-point instructions operate on single-precision and double-precision floating-point operands. The PowerPC Architecture uses instructions that are four bytes long and word-aligned. It provides for byte, halfword, word, and doubleword operand fetches and stores between storage and a set of 32 General Purpose Registers (GPRs). It also provides for word and doubleword operand fetches and stores between storage and a set of 32 Floating-Point Registers (FPRs).

Signed integers are represented in two's complement form.

There are no computational instructions that modify storage. To use a storage operand in a computation and then modify the same or another storage location, the contents of the storage operand must be loaded into a register, modified, and then stored back to the target location. Figure 1 is a logical representation of instruction processing. Figure 2 shows the registers of the PowerPC User Instruction Set Architecture.

Figure 1. Logical processing mode

Figure 2. Power PC user register set

## 1.7 Instruction formats

All instructions are four bytes long and word-aligned. Thus, whenever instruction addresses are presented to the processor (as in *Branch* instructions) the low-order two bits are ignored. Similarly, whenever the processor develops an instruction address the low-order two bits are zero.

Bits 0:5 always specify the opcode (OPCD, below). Many instructions also have an extended opcode (XO, below). The remaining bits of the instruction contain one or more fields as shown below for the different instruction formats.

The format diagrams given below show horizontally all valid combinations of instruction fields. The diagrams include instruction fields that are used only by instructions defined in Book II, *PowerPC Virtual Environment Architecture*, or in Book III, *PowerPC Operating Environment Architecture*.

#### Split Field Notation

In some cases an instruction field occupies more than one contiguous sequence of bits, or occupies one contiguous sequence of bits that are used in permuted order. Such a field is called a *split field*. In the format diagrams given below and in the individual instruction layouts, the name of a split field is shown in small letters, once for each of the contiguous sequences. In the RTL description of an instruction having a split field, and in certain other places where individual bits of a split field are identified, the name of the field in small letters represents the concatenation of the sequences from left to right. In all other places, the name of the field is capitalized and represents the concatenation of the sequences in some order, which need not be left to right, as described for each affected instruction.

## 1.7.1 I-Form

Figure 3. I instruction format

## 1.7.2 B-Form

Figure 4. B instruction format

## 1.7.3 SC-Form

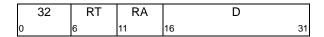

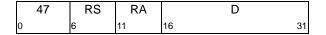

| 0    | 6   | 11  | 16 | 20  | 27 | 30 | 31 |

|------|-----|-----|----|-----|----|----|----|

| OPCD | /// | /// | // | LEV | // | 1  | /  |

Figure 5. SC instruction format

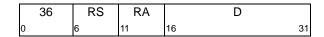

## 1.7.4 **D-Form**

| 0    | 6    |   | 11 | 16 31 |

|------|------|---|----|-------|

| OPCD | RT   |   | RA | D     |

| OPCD | RT   |   | RA | SI    |

| OPCD | RS   |   | RA | D     |

| OPCD | RS   |   | RA | UI    |

| OPCD | BF / | L | RA | SI    |

| OPCD | BF / | L | RA | UI    |

| OPCD | TO   |   | RA | SI    |

| OPCD | FRT  |   | RA | D     |

| OPCD | FRS  | ; | RA | D     |

Figure 6. D instruction format

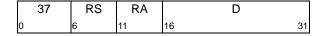

## 1.7.5 **DS-FORM**

| 0    | 6  | 11 | 16 | 30 31 |

|------|----|----|----|-------|

| OPCD | RT | RA | DS | XO    |

| OPCD | RS | RA | DS | XO    |

Figure 7. DS instruction format

## 1.7.6 X-FORM

| 0    | 6   |     | 11     | 16  | 21 | 31 |

|------|-----|-----|--------|-----|----|----|

| OPCD | R'  | Т   | RA     | RB  | XO | /  |

| OPCD | R'  | Т   | RA     | NB  | XO | /  |

| OPCD | R'  | Т   | / SR   | /// | XO | /  |

| OPCD | R'  | Т   | ///    | RB  | XO | /  |

| OPCD | R'  |     | ///    | /// | XO | /  |

| OPCD | R   | S   | RA     | RB  | XO | Rc |

| OPCD | R   | S   | RA     | RB  | XO | 1  |

| OPCD | R   | S   | RA     | RB  | XO | /  |

| OPCD | R   | S   | RA     | NB  | XO | /  |

| OPCD | R   | S   | RA     | SH  | XO | Rc |

| OPCD | R   | S   | RA     | /// | XO | Rc |

| OPCD | R   | S   | / SR   | /// | XO | /  |

| OPCD | R   | S   | ///    | RB  | XO | /  |

| OPCD | R   | S   | ///    | /// | XO | /  |

| OPCD | R   | S   | /// L  | /// | XO | /  |

| OPCD | BF  | / L | RA     | RB  | XO | /  |

| OPCD | BF  | //  | FRA    | FRB | XO | /  |

| OPCD | BF  | //  | BFA // | /// | XO | /  |

| OPCD | BF  | //  | ///    | U / | XO | Rc |

| OPCD | BF  | //  | ///    | /// | XO | /  |

| OPCD | / T | Н   | RA     | RB  | XO | /  |

| OPCD | /// | L   | RA     | RB  | XO | /  |

| OPCD | /// | L   | ///    | RB  | XO | /  |

| OPCD | /// | L   | ///    | /// | XO | /  |

| OPCD | TO  | )   | RA     | RB  | XO | /  |

| OPCD | FR  | RT. | RA     | RB  | XO | /  |

| OPCD | FR  | RT. | ///    | FRB | XO | Rc |

| OPCD | FR  | RT. | ///    | /// | XO | Rc |

| OPCD | FR  | S   | RA     | RB  | XO | /  |

| OPCD | В   | Т   | ///    | /// | XO | Rc |

| OPCD | //. |     | RA     | RB  | XO | /  |

| OPCD | //. | /   | ///    | RB  | XO | /  |

| OPCD | //. | /   | ///    | /// | XO | /  |

Figure 8. X instruction format

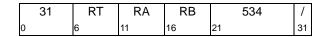

## 1.7.7 XL-FORM

| 0    | 6   |    | 11  |    | 16  |    | 21 | 31 |

|------|-----|----|-----|----|-----|----|----|----|

| OPCD | ВТ  |    | BA  | 4  | BI  | 3  | XO | /  |

| OPCD | BC  | )  | BI  |    | /// | ВН | XO | LK |

| OPCD | BF  | // | BFA | // | /// | /  | XO | /  |

| OPCD | /// | '  | /// | '  | /// | /  | XO | /  |

Figure 9. XL instruction format

## 1.7.8 **XFX-FORM**

| 0    | 6  | 11 |       | 21 | 31 |

|------|----|----|-------|----|----|

| OPCD | RT |    | spr   | XO | /  |

| OPCD | RT |    | tbr   | XO | /  |

| OPCD | RT | 0  | ///   | XO | /  |

| OPCD | RT | 1  | FXM / | XO | /  |

| OPCD | RS | 0  | FXM / | XO | /  |

| OPCD | RS | 1  | FXM / | XO | /  |

| OPCD | RS |    | spr   | XO | /  |

Figure 10. XFX instruction format

## 1.7.9 XFL-FORM

| 0  | 6    | 7   | 15 | 16  | 21 | 31   |

|----|------|-----|----|-----|----|------|

| OP | CD / | FLM | /  | FRB | XC | ) Rc |

Figure 11. XFL instruction format

## 1.7.10 XS-FORM

| ( | 0    | 6  | 11 | 16 | 21 | 30 | 31 |

|---|------|----|----|----|----|----|----|

|   | OPCD | RS | RA | sh | XO | sh | Rc |

Figure 12. XS instruction format

## 1.7.11 XO-FORM

| 0    | 6  | 11 | 16  | 21 | 22 | 31 |

|------|----|----|-----|----|----|----|

| OPCD | RT | RA | RB  | OE | XO | Rc |

| OPCD | RT | RA | RB  | /  | XO | Rc |

| OPCD | RT | RA | /// | OE | XO | Rc |

Figure 13. XO instruction format

#### 1.7.12 A-FORM

| 0    | 6   | 11  | 16  | 21  | 26 | 31 |

|------|-----|-----|-----|-----|----|----|

| OPCD | FRT | FRA | FRB | FRC | XO | Rc |

| OPCD | FRT | FRA | FRB | /// | XO | Rc |

| OPCD | FRT | FRA | /// | FRC | XO | Rc |

| OPCD | FRT | /// | FRB | /// | XO | Rc |

Figure 14. A instruction format

#### 1.7.13 M-FORM

| ( | )    | 6  | 11 | 16 | 21 | 26 | 31 |

|---|------|----|----|----|----|----|----|

| Ī | OPCD | RS | RA | RB | MB | ME | Rc |

| Ī | OPCD | RS | RA | SH | MB | ME | Rc |

Figure 15. M instruction format

### 1.7.14 MD-FORM

| 0    | 6  | 11 | 16 | 21 | 27 | 30 | 31 |

|------|----|----|----|----|----|----|----|

| OPCD | RS | RA | sh | mb | ΧO | sh | Rc |

| OPCD | RS | RA | sh | me | ΧO | sh | Rc |

Figure 16. MD instruction format

#### 1.7.15 MDS-FORM

| 0    | 6  | 11 | 16 | 21 | 27 | 31 |

|------|----|----|----|----|----|----|

| OPCD | RS | RA | RB | mb | XO | Rc |

| OPCD | RS | RA | RB | me | XO | Rc |

Figure 17. MDS instruction format

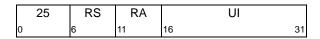

#### 1.7.16 Instruction Fields

#### AA (30)

Absolute Address bit.

- O The immediate field represents an address relative to the current instruction address. For I-form branches the effective address of the branch target is the sum of the LI field sign-extended to 64 bits and the address of the branch instruction. For B-form branches the effective address of the branch target is the sum of the BD field sign-extended to 64 bits and the address of the branch instruction.

- The immediate field represents an absolute address. For I-form branches the effective address of the branch target is the LI field sign-extended to 64 bits. For B-form branches the effective address of the branch target is the BD field sign-extended to 64 bits.

#### BA (11:15)

Field used to specify a bit in the CR to be used as a source.

#### BB (16:20)

Field used to specify a bit in the CR to be used as a source.

#### BD (16:29)

Immediate field used to specify a 14-bit signed two's complement branch displacement which is concatenated on the right with 0b00 and sign-extended to 64 bits.

#### BF (6:8)

Field used to specify one of the CR fields or one of the FPSCR fields to be used as a target.

#### BFA (11:13)

Field used to specify one of the CR fields or one of the FPSCR fields to be used as a source.

#### BH (19:20)

Field used to specify a hint in the *Branch Conditional to Link Register* and *Branch Conditional to Count Register* instructions. The encoding is described in Section 2.4.1, "Branch Instructions" on page 20.

#### BI (11:15)

Field used to specify a bit in the CR to be tested by a *Branch Conditional* instruction.

#### BO (6:10)

Field used to specify options for the *Branch Conditional* instructions. The encoding is described in Section 2.4.1, "Branch Instructions" on page 20.

#### BT (6:10)

Field used to specify a bit in the CR or in the FPSCR to be used as a target.

#### D (16:31)

Immediate field used to specify a 16-bit signed two's complement integer which is sign-extended to 64 bits.

#### DS (16:29)

Immediate field used to specify a 14-bit signed two's complement integer which is concatenated on the right with 0b00 and sign-extended to 64 bits.

#### FLM (7:14)

Field mask used to identify the FPSCR fields that are to be updated by the *mtfsf* instruction.

#### FRA (11:15)

Field used to specify an FPR to be used as a source.

#### FRB (16:20)

Field used to specify an FPR to be used as a source.

#### FRC (21:25)

Field used to specify an FPR to be used as a source.

#### FRS (6:10)

Field used to specify an FPR to be used as a source.

#### FRT (6:10)

Field used to specify an FPR to be used as a target.

#### FXM (12:19)

Field mask used to identify the CR fields that are to be written by the *mtcrf* and *mtocrf* instructions, or read by the *mfocrf* instruction.

#### L (10 or 15)

Field used to specify whether a fixed-point Compare instruction is to compare 64-bit numbers or 32-bit numbers.

Field used by the optional version of the *Data Cache Block Flush* instruction (see Book II, *PowerPC Virtual Environment Architecture*).

Field used by the *Move To Machine State Register* and *TLB Invalidate Entry* instructions (see Book III, *PowerPC Operating Environment Architecture*).

#### L (9:10)

Field used by the *Synchronize* instruction (see Book II, *PowerPC Virtual Environment Architecture*).

#### LEV (20:26)

Field used by the System Call instruction.

#### LI (6:29)

Immediate field used to specify a 24-bit signed two's complement integer which is concatenated on the right with 0b00 and sign-extended to 64 bits.

#### LK (31)

LINK bit.

- 0 Do not set the Link Register.

- Set the Link Register. The address of the instruction following the *Branch* instruction is placed into the Link Register.

#### MB (21:25) and ME (26:30)

Fields used in M-form instructions to specify a 64-bit mask consisting of 1-bits from bit MB+32 through bit ME+32 inclusive and 0-bits elsewhere, as described in Section 3.3.12, "Fixed-Point Rotate and Shift Instructions" on page 71.

#### MB (21:26)

Field used in MD-form and MDS-form instructions to specify the first 1-bit of a 64-bit mask, as described in Section 3.3.12, "Fixed-Point Rotate and Shift Instructions" on page 71.

#### ME (21:26)

Field used in MD-form and MDS-form instructions to specify the last 1-bit of a 64-bit mask, as described in Section 3.3.12, "Fixed-Point Rotate and Shift Instructions" on page 71.

#### NB (16:20)

Field used to specify the number of bytes to move in an immediate Move Assist instruction.

#### **OPCD (0:5)**

Primary opcode field.

#### OE (21)

Field used by XO-form instructions to enable setting OV and SO in the XER.

#### RA (11:15)

Field used to specify a GPR to be used as a source or as a target.

#### RB (16:20)

Field used to specify a GPR to be used as a source.

#### Rc (31)

RECORD bit.

- 0 Do not alter the Condition Register.

- 1 Set Condition Register Field 0 or Field 1 as described in Section 2.3.1, "Condition Register" on page 18.

#### RS (6:10)

Field used to specify a GPR to be used as a source.

#### RT (6:10)

Field used to specify a GPR to be used as a target.

#### SH (16:20, or 16:20 and 30)

Field used to specify a shift amount.

#### SI (16:31)

Immediate field used to specify a 16-bit signed integer.

#### SPR (11:20)

Field used to specify a Special Purpose Register for the *mtspr* and *mfspr* instructions.

#### SR (12:15)

Field used by the Segment Register Manipulation instructions (see Book III, PowerPC Operating Environment Architecture).

#### TBR (11:20)

Field used by the Move From Time Base instruction (see Book II, PowerPC Virtual Environment Architecture).

#### TH (7:10)

Field used by the optional data stream variant of the *dcbt* instruction (see Book II, *PowerPC Virtual Environment Architecture*).

#### TO (6:10)

Field used to specify the conditions on which to trap. The encoding is described in Section 3.3.10, "Fixed-Point Trap Instructions" on page 62.

#### U (16:19)

Immediate field used as the data to be placed into a field in the FPSCR.

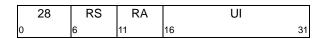

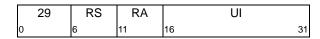

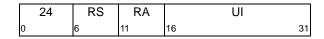

#### UI (16:31)

Immediate field used to specify a 16-bit unsigned integer.

# XO (21:29, 21:30, 22:30, 26:30, 27:29, 27:30, or 30:31)

Extended opcode field.

## 1.8 Classes of Instructions

An instruction falls into exactly one of the following three classes:

Defined

Illegal

Reserved

The class is determined by examining the opcode, and the extended opcode if any. If the opcode, or combination of opcode and extended opcode, is not that of a defined instruction or of a reserved instruction, the instruction is illegal.

#### 1.8.1 Defined Instruction Class

This class of instructions contains all the instructions defined in the PowerPC User Instruction Set Architecture, PowerPC Virtual Environment Architecture, and PowerPC Operating Environment Architecture.

In general, defined instructions are guaranteed to be provided in all implementations. The only exceptions are instructions that are optional instructions. These exceptions are identified in the instruction descriptions.

A defined instruction can have preferred and/or invalid forms, as described in Section 1.9.1, "Preferred Instruction Forms" and Section 1.9.2, "Invalid Instruction Forms".

## 1.8.2 Illegal Instruction Class

This class of instructions contains the set of instructions described in Appendix G, "Illegal Instructions" on page 187. Illegal instructions are available for future extensions of the PowerPC Architecture; that is, some future version of the PowerPC Architecture may define any of these instructions to perform new functions.

Any attempt to execute an illegal instruction will cause the system illegal instruction error handler to be invoked and will have no other effect.

An instruction consisting entirely of binary 0s is guaranteed always to be an illegal instruction. This increases the probability that an attempt to execute data or uninitialized storage will result in the invocation of the system illegal instruction error handler.

#### 1.8.3 Reserved Instruction Class

This class of instructions contains the set of instructions described in Appendix H, "Reserved Instructions" on page 189.

Reserved instructions are allocated to specific purposes that are outside the scope of the PowerPC Architecture.

Any attempt to execute a reserved instruction will:

- perform the actions described in Book IV, PowerPC Implementation Features for the implementation if the instruction is implemented; or

- cause the system illegal instruction error handler to be invoked if the instruction is not implemented.

# 1.9 Forms of Defined Instructions

#### 1.9.1 Preferred Instruction Forms

Some of the defined instructions have preferred forms. For such an instruction, the preferred form will execute in an efficient manner, but any other form may take significantly longer to execute than the preferred form.

Instructions having preferred forms are:

- the Condition Register Logical instructions

- the Load/Store Multiple instructions

- the *Load/Store String* instructions

- the Or Immediate instruction (preferred form of no-op)

- the Move To Condition Register Fields instruction

#### 1.9.2 Invalid Instruction Forms

Some of the defined instructions can be coded in a form that is invalid. An instruction form is invalid if one or more fields of the instruction, excluding the opcode field(s), are coded incorrectly in a manner that can be deduced by examining only the instruction encoding.

In general, any attempt to execute an invalid form of an instruction will either cause the system illegal instruction error handler to be invoked or yield boundedly undefined results. Exceptions to this rule are stated in the instruction descriptions.

Some instruction forms are invalid because the instruction contains a reserved value in a defined field (see Section 1.5.2 on page 3); these invalid forms are not discussed further. All other invalid forms are identified in the instruction descriptions.

#### Assembler Note -

Assemblers should report uses of invalid instruction forms as errors.

## 1.10 Optionality

Some of the defined instructions are optional. The optional instructions are defined in Chapter 5. "Optional Facilities and Instructions" on page 123. Additional optional instructions may be defined in Books II and III (e.g., see the section entitled "Lookaside Buffer Management" in Book III, and the chapters entitled "Optional Facilities and Instructions" in Book II and Book III).

Any attempt to execute an optional instruction that is not provided by the implementation will cause the system illegal instruction error handler to be invoked.

In addition to instructions, other kinds of optional facilities, such as registers, may be defined in Books II and III. The effects of attempting to use an optional facility that is not provided by the implementation are described in Books II and III as appropriate.

## 1.11 Exceptions

There are two kinds of exception, those caused directly by the execution of an instruction and those caused by an asynchronous event. In either case, the exception may cause one of several components of the system software to be invoked.

The exceptions that can be caused directly by the execution of an instruction include the following:

- an attempt to execute an illegal instruction, or an attempt by an application program to execute a "privileged" instruction (see Book III, PowerPC Operating Environment Architecture) (system illegal instruction error handler or system privileged instruction error handler)

- the execution of a defined instruction using an invalid form (system illegal instruction error handler or system privileged instruction error handler)

- the execution of an optional instruction that is not provided by the implementation (system illegal instruction error handler)

- an attempt to access a storage location that is unavailable (system instruction storage error handler or system data storage error handler)

- an attempt to access storage with an effective address alignment that is invalid for the instruction (system alignment error handler)

- the execution of a System Call instruction (system service program)

- the execution of a *Trap* instruction that traps (system trap handler)

- the execution of a floating-point instruction that causes a floating-point enabled exception to exist

(system floating-point enabled exception error handler)

The exceptions that can be caused by an asynchronous event are described in Book III, *PowerPC Operating Environment Architecture*.

The invocation of the system error handler is precise, except that if one of the imprecise modes for invoking the system floating-point enabled exception error handler is in effect (see page 96) then the invocation of the system floating-point enabled exception error handler may be imprecise. When the system error handler is invoked imprecisely, the excepting instruction does not appear to complete before the next instruction starts (because one of the effects of the excepting instruction, namely the invocation of the system error handler, has not yet occurred).

Additional information about exception handling can be found in Book III, *PowerPC Operating Environment Architecture*.

## 1.12 Storage Addressing

A program references storage using the effective address computed by the processor when it executes a *Storage Access* or *Branch* instruction (or certain other instructions described in Book II, *PowerPC Virtual Environment Architecture*, and Book III, *PowerPC Operating Environment Architecture*), or when it fetches the next sequential instruction.

## 1.12.1 Storage Operands

Bytes in storage are numbered consecutively starting with 0. Each number is the address of the corresponding byte.

Storage operands may be bytes, halfwords, words, or doublewords, or, for the *Load/Store Multiple* and *Move Assist* instructions, a sequence of bytes or words. The address of a storage operand is the address of its first byte (i.e., of its lowest-numbered byte). Byte ordering is Big-Endian. However, if the optional Little-Endian facility is implemented the system can be operated in a mode in which byte ordering is Little-Endian; see Section 5.3.

Operand length is implicit for each instruction.

The operand of a single-register *Storage Access* instruction has a "natural" alignment boundary equal to the operand length. In other words, the "natural" address of an operand is an integral multiple of the operand length. A storage operand is said to be *aligned* if it is aligned at its natural boundary; otherwise it is said to be *unaligned*.

Storage operands for single-register *Storage Access* instructions have the following characteristics. (Although not permitted as storage operands, quadwords are shown because quadword alignment is desirable for certain storage operands.)

| Operand    | Length   | Addr <sub>60:63</sub> if aligned |

|------------|----------|----------------------------------|

| Byte       | 8 bits   | xxxx                             |

| Halfword   | 2 bytes  | xxx0                             |

| Word       | 4 bytes  | xx00                             |

| Doubleword | 8 bytes  | x000                             |

| Quadword   | 16 bytes | 0000                             |

**Note:** An "x" in an address bit position indicates that the bit can be 0 or 1 independent of the state of other bits in the address.

The concept of alignment is also applied more generally, to any datum in storage. For example, a 12-byte datum in storage is said to be word-aligned if its address is an integral multiple of 4.

Some instructions require their storage operands to have certain alignments. In addition, alignment may affect performance. For single-register *Storage Access* instructions the best performance is obtained when storage operands are aligned. Additional effects of data placement on performance are described in Book II, *PowerPC Virtual Environment Architecture*.

Instructions are always four bytes long and word-aligned.

# 1.12.2 Effective Address Calculation

An effective address is computed by the processor when executing a *Storage Access* or *Branch* instruction (or certain other instructions described in Book II, *PowerPC Virtual Environment Architecture*, and Book III, *PowerPC Operating Environment Architecture*) or when fetching the next sequential instruction. The following provides an overview of this process. More detail is provided in the individual instruction descriptions.