Software Development Kit for Multicore Acceleration Version 3.1

# Programmer's Guide

Software Development Kit for Multicore Acceleration Version 3.1

# Programmer's Guide

Note: Before using this information and the product it supports, read the general information in "Notices" on page 95.

#### **Edition Notice**

This edition applies to the version 3, release 1, modification 0 of the IBM Software Development Kit for Multicore Acceleration (Product number 5724-S84) and to all subsequent releases and modifications until otherwise indicated in new editions.

| This edition replaces SC33-8325-02.

#### © Copyright International Business Machines Corporation 2006, 2008.

US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

## Contents

|   | Preface                                           | . v  |

|---|---------------------------------------------------|------|

|   | About this book                                   |      |

|   | What's new for SDK 3.1                            |      |

|   | Supported operating environments                  | . vi |

|   | Supported hardware requirements                   | . vi |

|   | Software requirements                             |      |

|   | Software requirements                             | vi   |

|   | Getting support                                   |      |

|   | Related documentation                             | vii  |

|   |                                                   |      |

|   | Chapter 1. SDK technical overview                 | . 1  |

|   | GNU tool chain                                    |      |

|   | IBM XL C/C++ compiler                             | 2    |

|   | Linux kernel                                      | . 2  |

|   | Linux kernel                                      | . 3  |

|   | SPE Runtime Management Library Version 2.3 .      | . 3  |

|   | SIMD math libraries                               | . 5  |

|   | Mathematical Acceleration Subsystem (MASS)        | . 4  |

|   |                                                   | 4    |

|   | libraries                                         | . 4  |

|   |                                                   | . 5  |

|   | DaCS library                                      | . 5  |

| I | Fast Fourier Transform library                    |      |

|   | Monte Carlo libraries                             | . 6  |

| ! | Basic Linear Algebra Sublibrary                   | . 7  |

| I | LAPACK library                                    | . 7  |

|   | Code examples and example libraries               | . 8  |

|   | Performance tools                                 | . 11 |

|   | IBM Eclipse IDE for the SDK                       |      |

|   | Overview of the hybrid programming environment    | 12   |

|   | Chapter 2 Programming with the CDK                | 13   |

|   | Chapter 2. Programming with the SDK               |      |

|   |                                                   | 13   |

|   | Specifying the processor architecture             | 13   |

|   |                                                   | 15   |

|   |                                                   | 15   |

|   | Changing the build environment                    |      |

|   | Building and running a specific program           |      |

|   | Compiling and linking with the GNU tool chain     |      |

|   | Developing applications with the SDK              | 17   |

| I | SDK programming policies and conventions .        | 18   |

|   | Managing a DMA list element crossing 4 GB         |      |

| L | boundary                                          | 19   |

|   | Performance considerations                        | 20   |

|   | Using the huge translation lookaside buffer (TLB) |      |

|   | to reserve memory                                 |      |

|   |                                                   | 21   |

|   | 0                                                 | 22   |

|   | 1 0                                               |      |

|   | Chapter 3. Debugging Cell/B.E.                    |      |

|   | annlications                                      | 23   |

| applications                       | 23   |

|------------------------------------|------|

| Overview of GDB                    | . 23 |

| GDB for SDK                        | . 23 |

| Compiling and linking applications | . 23 |

| Debugging applications             | . 24 |

| Debugging PPE code                 | . 24 |

|   | Debugging SPE code                          | . 31                                                                                                                                                              |

|---|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Debugging multithreaded code                | . 32                                                                                                                                                              |

|   | Using the combined debugger                 | . 36                                                                                                                                                              |

|   | New command reference                       | . 41                                                                                                                                                              |

|   | Debugging applications remotely             | . 43                                                                                                                                                              |

|   | Overview of remote debugging                | . 43                                                                                                                                                              |

|   | Using remote debugging                      | . 44                                                                                                                                                              |

|   | Starting remote debugging                   | . 44                                                                                                                                                              |

| I | Chapter 4. Debugging common Direct          |                                                                                                                                                                   |

| L | Memory Access (DMA) errors                  | . 47                                                                                                                                                              |

| L |                                             |                                                                                                                                                                   |

| L | DMA errors                                  | . 48                                                                                                                                                              |

| L | Examples                                    | . 50                                                                                                                                                              |

| L | Unaligned effective address                 | . 50                                                                                                                                                              |

| L | Tag ID errors    .    .    .    .    .    . | . 52                                                                                                                                                              |

| L | Transfer size errors                        | . 53                                                                                                                                                              |

| L | Unaligned local store address               | . 57                                                                                                                                                              |

| L | Segmentation faults                         |                                                                                                                                                                   |

| L | DMA list element crossing 4 GB boundary     | . 59                                                                                                                                                              |

| L | DMA race conditions                         | . 60                                                                                                                                                              |

| I | Chapter 5. Using the SPU GNU profiler       | 63                                                                                                                                                                |

|   | <b>3</b>                                    |                                                                                                                                                                   |

|   | Chapter 6. Analyzing Cell/B.E. SPUs         | ~                                                                                                                                                                 |

|   | with kdump and crash                        | 67                                                                                                                                                                |

|   |                                             |                                                                                                                                                                   |

|   | Installation requirements                   | . 67                                                                                                                                                              |

|   | Installation requirements                   | . 67<br>. 68                                                                                                                                                      |

|   | Installation requirements                   | . 67<br>. 68                                                                                                                                                      |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b>                                                                                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71                                                                                                                         |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71                                                                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72                                                                                                         |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72                                                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72                                                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                                              |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                                              |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73                                                                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76                         |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77                 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 79         |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 79         |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 79<br>. 80 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 79<br>. 80 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br><b>71</b><br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 79<br>. 80 |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                              |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                              |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                              |

|   | Installation requirements                   | . 67<br>. 68<br>. 68<br>. 71<br>. 71<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 72                                                              |

| Generating automatic overlay scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A. Related documentation 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Appendix B. Accessibility features 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Notices         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . </td |

Ι

| Terms and conditions | 7 |

|----------------------|---|

| Glossary             | 9 |

| Index                | 9 |

## Preface

|

I

I

I

|

The IBM Software Development Kit for Multicore Acceleration Version 3.1 (SDK) is a complete package of tools to enable you to program applications for the Cell Broadband Engine<sup>™</sup> (Cell/B.E.) processor. The SDK is composed of development tool chains, software libraries and sample source files, and a Linux<sup>®</sup> kernel, all of which fully support the capabilities of the Cell/B.E..

- Chapter 1, "SDK technical overview," on page 1 describes the components of the SDK

- Chapter 2, "Programming with the SDK," on page 13 explains how to program applications for the Cell/B.E. platform

- Chapter 3, "Debugging Cell/B.E. applications," on page 23 describes how to debug your applications

- Chapter 4, "Debugging common Direct Memory Access (DMA) errors," on page 47

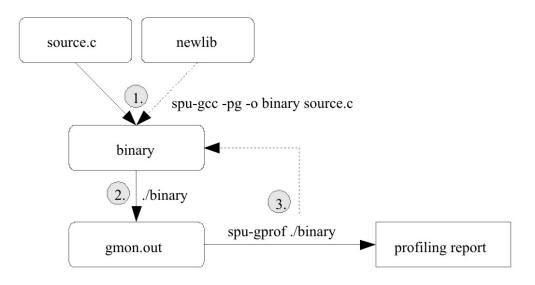

- Chapter 5, "Using the SPU GNU profiler," on page 63 describes how to sue the SPU GNU profiler tool

- Chapter 6, "Analyzing Cell/B.E. SPUs with kdump and crash," on page 67 describes a means of debugging kernel data related to SPUs through specific crash commands, by using a dumped kernel image.

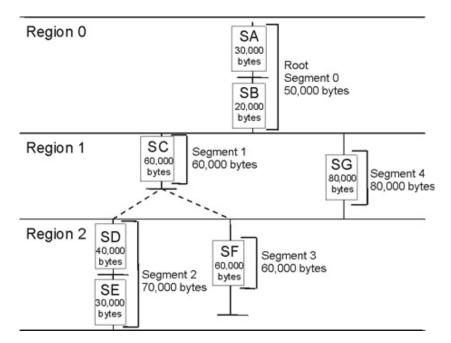

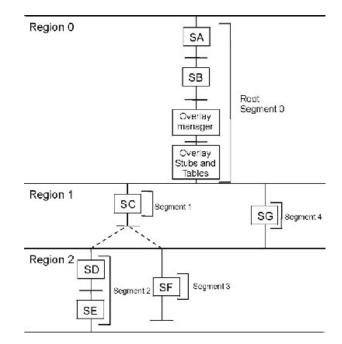

- Chapter 7, "Using SPU code overlays," on page 71 describes how to use overlays

## About this book

This book describes how to use the SDK to write applications. How to install SDK is described in a separate manual, *Software Development Kit for Multicore Acceleration Installation Guide*, and there is also a programming tutorial to help get you started.

## What's new for SDK 3.1

This book includes information about the new functionality delivered with the SDK, and completely replaces the previous version of this book.

This new information includes:

- Information about sharing of MFC tag identifiers, sharing MFC tag masks, and interrupt safe MFC command requests, see "SDK programming policies and conventions" on page 18

Chapter 4, "Debugging common Direct Memory Access (DMA) errors," on page 47

GDB usability enhancements, see "Multi-location breakpoints" on page 37

For the combined debugger, information about a new facility for symbol determination, see "Disambiguation of multiply-defined global symbols" on page 39

There are now two versions of the gdbserver debugger, see "Debugging applications remotely" on page 43

How to generate automatic overlays, see "Generating automatic overlay scripts" on page 89

- How to use the SPU GNU profiler, see Chapter 5, "Using the SPU GNU profiler," on page 63

• Performance-tool related information has been removed from this book and is now located in the *Performance Tools Guide*

## Supported operating environments

Т

T

T

This topic describes the SDK hardware and software requirements.

### Supported hardware requirements

This topic describes the supported hardware requirements.

Cell/B.E. applications can be developed on the following platforms:

- x86

- x86-64

- 64-bit PowerPC<sup>®</sup> (PPC64)

- IBM BladeCenter QS21

- IBM BladeCenter QS22

#### Software requirements

This topic describes the SDK software requirements.

The supported languages are:

- C/C++

- Assembler

- Fortran

- ADA (Power Processing Element (PPE) Only)

**Note:** Although C++ and Fortran are supported, take care when you write code for the Synergistic Processing Units (SPUs) because many of the C++ and Fortran libraries are too large for the 256 KB local storage memory available.

#### **Unsupported beta-level environments**

This publication contains documentation that may be applied to certain environments on an "as-is" basis. Those environments are not supported by IBM, but wherever possible, work-arounds to problems are provided in the respective forums. The following libraries and utilities are provided on an "as-is" basis:

- ALF for Hybrid

- DaCS for Hybrid

- Hybrid Performance Tools

- 3D Fast Fourier Transform Library

- SPU Timing

- Security Toolkit Isolation, Crypto Library

- CPC RHEL user tool

- CPC Fedora user tool

- IBM BladeCenter<sup>®</sup> QS20

### Getting support

The SDK is available through Passport Advantage<sup>®</sup> with full support at: http://www.ibm.com/software/passportadvantage

You can locate documentation and other resources on the World Wide Web. Refer to the following Web sites:

• IBM BladeCenter systems, optional devices, services, and support information at http://www.ibm.com/bladecenter/

For service information, select Support.

developerWorks<sup>®</sup> Cell BE Resource Center at: http://www.ibm.com/developerworks/power/cell/

To access the Cell BE forum on developerWorks, select Community.

- The Barcelona Supercomputing Center (BSC) Web site at http://www.bsc.es/projects/deepcomputing/linuxoncell

- There is also support for the Full-System Simulator and XL C/C++ Compiler through their individual alphaWorks<sup>®</sup> forums. If in doubt, start with the Cell BE architecture forum.

- The GNU Project debugger, GDB is supported through many different forums on the Web, but primarily at the GDB Web site http://www.gnu.org/software/gdb/gdb.html

This version of the SDK supersedes all previous versions of the SDK.

## **Related documentation**

For a list of documentation referenced in this *Programmer's Guide*, see Appendix B. Related documentation.

## Chapter 1. SDK technical overview

This section describes the contents of the SDK, where it is installed on the system, and how the various components work together.

It covers the following topics:

- "GNU tool chain"

- "IBM XL C/C++ compiler" on page 2

- "Linux kernel" on page 3

- "Libraries and frameworks" on page 3

- "Performance tools" on page 11

- "IBM Eclipse IDE for the SDK" on page 11

- "Overview of the hybrid programming environment" on page 12

## **GNU** tool chain

This topic provides an overview of the GNU tool chain.

| <br> <br> | The GNU tool chain contains the GNU Compiler Collection compilers for the C, C++, and Fortran programming languages (gcc, g++, and gfortran) for the PPU and the SPU. For the PPU it is a replacement for the native GCC compiler on PowerPC (PPC) platforms and it is a cross-compiler on X86. The GCC compiler for the PPU is the default and the Makefiles are configured to use it when building the libraries and samples. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | The GCC compiler also contains a separate SPE cross-compiler that supports the standards defined in the following documents:                                                                                                                                                                                                                                                                                                    |

| I         | • C/C++ Language Extensions for Cell Broadband Engine Architecture V2.6. The GCC compiler shipped in SDK supports all language extension described in the specification except for the following:                                                                                                                                                                                                                               |

|           | <ul> <li>The GCC compilers currently do not support alignment of stack variables<br/>greater than 16 bytes as described in section 1.3.1.</li> </ul>                                                                                                                                                                                                                                                                            |

|           | <ul> <li>The GCC compilers currently do not support the optional alternate vector<br/>literal format specified in section 1.4.6.</li> </ul>                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>The GCC compilers currently support mapping between SPU and VMX<br/>intrinsics as defined in section 5 only in C++ code.</li> </ul>                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>The recommended vector printf format controls as specified in section 8.1.1<br/>due to library restrictions.</li> </ul>                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>The GCC compiler does not support the optional Altivec style of vector literal construction using parenthesis ("(" and ")"). The standard C method of array initialization using curly braces ("{" and "}") should be used.</li> </ul>                                                                                                                                                                                 |

|           | <ul> <li>The C99 complex math library as specified in section 8.1.1 due to library restrictions</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| <br> <br> | <ul> <li>The GCC compiler currently does not support the Vector Shift Right and<br/>Quadword Shift Right families of the SPU intrinsics (spu_sr, spu_sra, spu<br/>srqw, spu_srqwbyte, spu_srqwbytebc)</li> </ul>                                                                                                                                                                                                                |

|           | • SPU Application Binary Interface (ABI) Specification V1.9                                                                                                                                                                                                                                                                                                                                                                     |

|           | • SPU Instruction Set Architecture V1.2                                                                                                                                                                                                                                                                                                                                                                                         |

The associated assembler and linker additionally support the *SPU Assembly Language Specification V1.7*. The assembler and linker are common to both the GCC compiler and the "IBM XL C/C++ compiler."

GDB support is provided for both PPU and SPU debugging, and the debugger client can be in the same process or a remote process. GDB also supports combined (PPU and SPU) debugging.

On a non-PPC system, the install directory for the GNU tool chain is /opt/cell/toolchain. There is a single bin subdirectory, which contains both PPU and SPU tools.

On a PPC64 or an IBM BladeCenter QS21, or IBM BladeCenter QS22, both tool chains are installed into /usr. See "SDK directories" on page 13 for further information.

## IBM XL C/C++ compiler

|

T

T

I

IBM XL C/C++ for Multicore Acceleration for Linux is an advanced, high-performance cross-compiler that is tuned for the CBEA.

The XL C/C++ compiler, which is hosted on an x86, IBM PowerPC technology-based system, or a IBM BladeCenter QS21, or IBM BladeCenter QS22, generates code for the PPU or SPU. The compiler requires the GCC toolchain for the CBEA, which provides tools for cross-assembling and cross-linking applications for both the PPE and SPE.

IBM XL C/C++ supports the revised 2003 International C++ Standard *ISO/IEC* 14882:2003(*E*), *Programming Languages* -- C++ and the *ISO/IEC* 9899:1999, *Programming Languages* -- C standard, also known as C99. The compiler also supports:

- The C89 Standard and K & R style of programming

- Language extensions for vector programming

- Language extensions for SPU programming

- Numerous GCC C and C++ extensions to help users port their applications from GCC.

The XL C/C++ compiler available for the SDK supports the languages extensions as specified in the *IBM XL C/C++ Advanced Edition for Multicore Acceleration for Linux Language Reference*.

The XL compiler also contains a separate SPE cross-compiler that supports the standards defined in the following documents:

- C/C++ Language Extensions for Cell Broadband Engine Architecture V2.6. The XL compiler shipped in SDK supports all language extension described in the specification except for the following:

- The XL compilers currently do not support the \_\_builtin\_expect\_call builtin function call

- The XL compilers currently support mapping between SPU and VMX intrinsics as defined in section 5 only in C++ code

- The recommended vector printf format controls as specified in section 8.1.1 due to library restrictions

- The C99 complex math library as specified in section 8.1.1 due to library restrictions

|   | - The SPU XL compilers currently do not support the Vector Shift Right and |

|---|----------------------------------------------------------------------------|

|   | Quadword Shift Right families of the SPU intrinsics (spu_sr, spu_sra, spu  |

|   | srqw, spu_srqwbyte, spu_srqwbytebc)                                        |

| • | SPU Application Binary Interface (ABI) Specification Version 1.9           |

| • | SPU Instruction Set Architecture Version 1.2                               |

| _ |                                                                            |

| • |                                                                            |

For information about the XL C/C++ compiler invocation commands and a complete list of options, refer to the *IBM XL C/C++ Advanced Edition for Multicore Acceleration for Linux Programming Guide*.

Program optimization is described in *IBM XL C/C++ Advanced Edition for Multicore Acceleration for Linux Programming Guide.*

The XL C/C++ for Multicore Acceleration for Linux compiler is installed into the/opt/ibmcmp/xlc/cbe/<compiler version number> directory. Documentation is located on the following Web site:

http://publib.boulder.ibm.com/infocenter/cellcomp/v9v111/index.jsp

## Linux kernel

L

L

For the IBM IBM BladeCenter QS21 and IBM BladeCenter QS22, the kernel is installed into the /boot directory, yaboot.conf is modified and a reboot is required to activate this kernel.

The cellsdk install task is documented in the SDK Installation Guide.

**Note:** The cellsdk uninstall command does not automatically uninstall the kernel. This avoids leaving the system in an unusable state.

## Libraries and frameworks

This topic provides a brief overview of the Cell/B.E. libraries.

The following libraries are described:

- "SPE Runtime Management Library Version 2.3"

- "SIMD math libraries" on page 4

- "Mathematical Acceleration Subsystem (MASS) libraries" on page 4

- "ALF library" on page 5

- "DaCS library" on page 5

## **SPE Runtime Management Library Version 2.3**

The SPE Runtime Management Library (libspe) constitutes the standardized low-level application programming interface (API) for application access to the Cell/B.E. SPEs.

This library provides an API to manage SPEs that is neutral with respect to the underlying operating system and its methods. Implementations of this library can provide additional functionality that allows for access to operating system or implementation-dependent aspects of SPE runtime management. These capabilities are not subject to standardization and their use may lead to non-portable code and dependencies on certain implemented versions of the library.

The elfspe is a PPE program that allows an SPE program to run directly from a Linux command prompt without needing a PPE application to create an SPE thread and wait for it to complete.

For the IBM BladeCenter QS21 and IBM BladeCenter QS22, the SDK installs the libspe headers, libraries, and binaries into the /usr directory and the standalone SPE executive, elfspe, is registered with the kernel during boot by commands added to /etc/rc.d/init.d using the binfmt\_misc facility.

For the simulator, the libspe and elfspe binaries and libraries are preinstalled in the same directories in the system root image and no further action is required at install time.

## SIMD math libraries

The SIMD math library provides short vector versions of the math functions.

The traditional math functions are scalar instructions, and do not take advantage of the powerful Single Instruction, Multiple Data (SIMD) vector instructions available in both the PPU and SPU in the Cell/B.E. Architecture. SIMD instructions perform computations on short vectors of data in parallel, instead of on individual scalar data elements. They often provide significant increases in program speed because more computation can be done with fewer instructions.

While the SIMD math library provides short vector versions of math functions, the MASS library provides long vector versions. These vector versions conform as closely as possible to the specifications set out by the scalar standards.

The SIMD math library is provided by the SDK as both a linkable library archive and as a set of inline function headers. The names of the SIMD math functions are formed from the names of the scalar counterparts by appending a vector type suffix to the standard scalar function name. For example, the SIMD version of the absolute value function abs(), which acts on a vector of long integers, is called absi4(). Inline versions of functions are prefixed with the character "\_" (underscore), so the inline version of absi4() is called \_absi4().

For more information about the SIMD math library, refer to SIMD Math Library Specification for Cell Broadband Engine Architecture Version 1.1.

## Mathematical Acceleration Subsystem (MASS) libraries

The Mathematical Acceleration Subsystem (MASS) consists of libraries of mathematical intrinsic functions, which are tuned specifically for optimum performance on the Cell/B.E. processor.

Currently the 32-bit, 64-bit PPU, and SPU libraries are supported. These libraries:

- Include both scalar and vector functions

- Are thread-safe

- Support both 32- and 64-bit compilations

- Offer improved performance over the corresponding standard system library routines

- Are intended for use in applications where slight differences in accuracy or handling of exceptional values can be tolerated

You can find information about using these libraries on the MASS Web site: http://www.ibm.com/software/awdtools/mass

## ALF library

The ALF provides a programming environment for data and task parallel applications and libraries.

The ALF API provides library developers with a set of interfaces to simplify library development on heterogenous multi-core systems. Library developers can use the provided framework to offload computationally intensive work to the accelerators. More complex applications can be developed by combining the several function offload libraries. Application programmers can also choose to implement their applications directly to the ALF interface.

ALF supports the multiple-program-multiple-data (MPMD) programming module where multiple programs can be scheduled to run on multiple accelerator elements at the same time.

The ALF functionality includes:

- Data transfer management

- Parallel task management

- Double buffering

- Dynamic load balancing

With the provided platform-independent API, you can also create descriptions for multiple compute tasks and define their ordering information execution orders by defining task dependency. Task parallelism is accomplished by having tasks without direct or indirect dependencies between them. The ALF runtime provides an optimal parallel scheduling scheme for the tasks based on given dependencies.

From the application or library programmer's point of view, ALF consists of the following two runtime components:

- A host runtime library

- An accelerator runtime library

The host runtime library provides the host APIs to the application. The accelerator runtime library provides the APIs to the application's accelerator code, usually the computational kernel and helper routines. This division of labor enables programmers to specialize in different parts of a given parallel workload.

The runtime framework handles the underlying task management, data movement, and error handling, which means that the focus is on the kernel and the data partitioning, not the direct memory access (DMA) list creation or the lock management on the work queue.

The ALF APIs are platform-independent and their design is based on the fact that many applications targeted for Cell/B.E. or multi-core computing follow the general usage pattern of dividing a set of data into self-contained blocks, creating a list of data blocks to be computed on the SPE, and then managing the distribution of that data to the various SPE processes. This type of control and compute process usage scenario, along with the corresponding work queue definition, are the fundamental abstractions in ALF.

## **DaCS** library

The DaCS library provides a set of services for handling process-to-process communication in a heterogeneous multi-core system.

In addition to the basic message passing service these include:

- Mailbox services

- Resource reservation

- · Process and process group management

- Process and data synchronization

- Remote memory services

- Error handling

The DaCS services are implemented as a set of APIs providing an architecturally neutral layer for application developers. These APIs are available in both the C and Fortran programming languages. They structure the processing elements, referred to as DaCS Elements (DE), into a hierarchical topology. This includes general purpose elements, referred to as Host Elements (HE), and special processing elements, referred to as Accelerator Elements (AE). Host elements usually run a full operating system and submit work to the specialized processes which run in the Accelerator Elements.

Fast Fourier Transform library The Fast Fourier Transform (FFT) library handles a wide range of FFTs. It consists of the following: • API for the following routines used in single precision: - FFT Real -> Complex 1D FFT Complex-Complex 1D FFT Complex -> Real 1D - FFT Complex-Complex 2D for frequencies (from 1000x1000 to 2500x2500) The implementation manages sizes up to 10000 and handles multiples of 2, 3, and 5 as well as powers of those factors, plus one arbitrary factor as well. User code running on the PPU makes use of the CBE FFT library by calling one of either 1D or 2D streaming functions. Power-of-two-only 2D FFT code for complex-to-complex single and double precision processing. Both parts of the library run using a common interface that contains an initialization and termination step, and an execution step which can process "one-at-a-time" requests (streaming) or entire arrays of requests (batch). Monte Carlo libraries The Monte Carlo libraries are a Cell/B.E. implementation of Random Number Generator (RNG) algorithms and transforms. The objective of this library is to provide functions needed to perform Monte Carlo simulations.

The following RNG algorithms are implemented:

- Hardware-based

- Kirkpatrick-Stoll

- Mersenne Twister

- Sobol

The following transforms are provided:

- Box-Mueller

- Moro's Inversion

Т

1

T

• Polar Method

L

I

I

I

I

1

L

1

L

1

L

1

I

I

L

I

I

L

T

I

Τ

1

I

T

L

I

|

## Basic Linear Algebra Sublibrary

This topic provides a short overview of the Basic Linear Algebra Sublibrary (BLAS).

The BLAS library is based upon a published standard interface, see the BLAS Technical Forum Standard document available at

http://www.netlib.org/blas/blast-forum/blas-report.pdf

for commonly-used linear algebra operations in high-performance computing (HPC) and other scientific domains.

It is widely used as the basis for other high quality linear algebra software, for example LAPACK and ScaLAPACK. The Linpack (HPL) benchmark largely depends on a single BLAS routine (DGEMM) for good performance.

The BLAS APIs are available as standard ANSI C and standard FORTRAN 77/90 interfaces. BLAS implementations are also available in open-source (netlib.org). Based on their functionality, BLAS routines are categorized into the following three levels:

- Level 1 routines are for scalar and vector operations

- Level 2 routines are for matrix-vector operations

- Level 3 routines are for matrix-matrix operations

BLAS routines can have up to four versions – real single precision, real double precision, complex single precision and complex double precision, represented by prefixing S, D, C and Z respectively to the routine name.

The BLAS library in the SDK supports only real single precision (SP) and real double precision (DP) versions. All SP and DP routines in the three levels of standard BLAS are supported on the Power Processing Element (PPE). These are available as PPE APIs and conform to the standard BLAS interface. (Refer to http://www.netlib.org/blas/blasqr.pdf)

Some of these routines have been optimized using the Synergistic Processing Elements (SPEs) and these exhibit substantially better performance in comparison to the corresponding versions implemented solely on the PPE. An SPE interface in addition to the PPE interface is provided for some of these routines; however, the SPE interface does not conform to the standard BLAS interface and provides a restricted version of the standard BLAS interface.

## LAPACK library

The LAPACK (Linear Algebra Package) library is based upon a published standard interface for commonly used linear algebra operations in high performance computing (HPC) and other scientific domains.

The LAPACK API is available with standard ANSI C and standard FORTRAN 77 interfaces. LAPACK implementations are also available as open source from http://netlib.org.

Each LAPACK routine has up to four versions, as detailed in the following table:

Table 1. LAPACK routine precision

|

Т

1

| Precision                | Routine name prefix |

|--------------------------|---------------------|

| Real single precision    | S                   |

| real double precision    | D                   |

| complex single precision | С                   |

| complex double precision | Z                   |

The LAPACK library in the SDK supports only real double precision, hereafter referred to as *DP*. All DP routines are available as PPE APIs and conform to the standard LAPACK FORTRAN 77 interface.

The following routines have been optimized to use features of the Synergistic Processing Elements (SPEs):

- DGETRF Compute the LU factorization of a general matrix

- DGETRI Compute the inverse of a general matrix using the LU factorization

- DGEQRF Compute the QR factorization of a general matrix

- DPOTRF Compute the Cholesky factorization of a symmetric positive matrix

- DBDSQR Compute the singular value decomposition of a real bi-diagonal matrix using the implicit zero-shift QR algorithm

- DSTEQR Compute the singular value decomposition of a real symmetric tridiagonal matrix using the implicit QR algorithm

### Code examples and example libraries

The example libraries package provides a set of optimized library routines that greatly reduce the development cost and enhance the performance of Cell/B.E. programs.

To demonstrate the versatility of the Cell/B.E. architecture, a variety of application-oriented libraries are included, such as:

- Fast Fourier Transform (FFT)

- Image processing

- Software managed cache

- Game math

- Matrix operation

- Multi-precision math

- Synchronization

- Vector

Additional examples and demos show how you can exploit the on-chip computational capacity.

Both the binary and the source code are shipped in separate RPMs. The RPM names are:

- cell-libs

- cell-examples

- cell-demos

- cell-tutorial

For each of these, there is one RPM that has the binaries - already built versions, that are installed into /opt/cell/sdk/usr, and for each of these, there is one RPM that has the source in a tar file. For example, cell-demos-source-3.0-1.rpm has demos source.tar and this tar file contains all of the source code.

The default installation process installs the binaries and installs the source tar files. You need to decide into which directory you want to untar those files, either into /opt/cell/sdk/src, or into a 'sandbox' directory.

The libraries and examples RPMs have been partitioned into the following subdirectories.

| Subdirectory                                                                  | Description                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /opt/cell/sdk/buildutils                                                      | Contains a README and the make include files (make.env, make.header, make.footer) that define the SDK build environment.                                                                                                                                                                                                                             |

| /opt/cell/sdk/docs                                                            | Contains all documentation, including information about SDK libraries and tools.                                                                                                                                                                                                                                                                     |

| /opt/cell/sdk/usr/bin<br>/opt/cell/sdk/usr/spu/bin                            | Contains executable programs for that platform. On an x86 system, this includes the SPU Timing tool. On a PPC system, this also includes all of the prebuilt binaries for the SDK examples (if installed). In the SDK build environment (that is, with buildutils/make.footer) the \$SDKBIN_ <target> variables point to these directories.</target> |

| /opt/cell/sdk/usr/include<br>/opt/cell/sdk/usr/spu/include                    | Contains header files for the SDK libraries and examples on a PPC system. In the SDK build environment (that is, with the buildutils/make.footer) the \$SDKINC_ <target> variables point to these directories.</target>                                                                                                                              |

| /opt/cell/sdk/usr/lib<br>/opt/cell/sdk/usr/lib64<br>/opt/cell/sdk/usr/spu/lib | Contains library binary files for the SDK libraries on a PPC system. In the SDK build environment (that is, with the buildutils/make.footer) the \$SDKLIB_ <target> variables point to these directories.</target>                                                                                                                                   |

| /opt/cell/sdk/src                                                             | Contains the tar files for the libraries and examples (if installed). The tar files are unpacked into the subdirectories described in the following rows of this table. Each directory has a README that describes their contents and purpose.                                                                                                       |

| /opt/cell/sdk/src/lib                                                         | Contains a series of libraries and reusable header files. Complete documentation for all library functions is in the /opt/cell/sdk/docs/lib/SDK_Example_Library_API_v3.1.pdf file.                                                                                                                                                                   |

Table 2. Subdirectories for the libraries and examples RPM

Table 2. Subdirectories for the libraries and examples RPM (continued)

| Subdirectory                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /opt/cell/sdk/src/examples   | The examples directory contains examples of Cell/B.E. programming<br>techniques. Each program shows a particular technique, or set of<br>related techniques, in detail. You can review these programs when<br>you want to perform a specific task, such as double-buffered DMA<br>transfers to and from a program, performing local operations on an<br>SPU, or provide access to main memory objects to SPU programs.                                                                                                                                                                                                                                           |

|                              | Some subdirectories contain multiple programs. The sync subdirectory has examples of various synchronization techniques, including mutex operations and atomic operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | The spulet model is intended to encourage testing and refinement of<br>programs that need to be ported to the SPUs; it also provides an easy<br>way to build filters that take advantage of the huge computational<br>capacity of the SPUs, while reading and writing standard input and<br>output.                                                                                                                                                                                                                                                                                                                                                              |

|                              | Other samples worth noting are:<br>• Overlay samples<br>• SW managed cache samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| /opt/cell/sdk/src/tutorial   | Contains tutorial code samples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| /opt/cell/sdk/src/demos      | The demo directory provides a handful of examples that can be used<br>to better understand the performance characteristics of the Cell/B.E.<br>processor. There are sample programs, which contain insights into<br>how real-world code should run.<br><b>Note:</b> Running these examples using the simulator takes much longer<br>than on the native Cell/B.Ebased hardware. The performance<br>characteristics in wall-clock time using the simulator are extremely<br>inaccurate, especially when running on multiple SPUs. You need to<br>examine the emulator CPU cycle counts instead.                                                                    |

|                              | For example, the matrix_mul program lets you perform matrix<br>multiplications on one or more SPUs. Matrix multiplication is a good<br>example of a function which the SPUs can accelerate dramatically.<br>Unlike some of the other example programs, these examples have<br>been tuned to get the best performance. This makes them harder to<br>read and understand, but it gives an idea for the type of performance<br>code that you can write for the Cell/B.E. processor.                                                                                                                                                                                 |

| /opt/cell/sdk/src/benchmarks | The benchmarks directory contains sample benchmarks for various<br>operations that are commonly performed in Cell/B.E. applications.<br>The intent of these benchmarks is to guide you in the design,<br>development, and performance analysis of applications for systems<br>based on the Cell/B.E. processor. The benchmarks are provided in<br>source form to allow you to understand in detail the actual operations<br>that are performed in the benchmark. This also provides you with a<br>basis for creating your own benchmark codes to characterize<br>performance for operations that are not currently covered in the<br>provided set of benchmarks. |

| /opt/cell/sdk/prototype/src  | Contains the tar files for examples and demos for various prototype packages that ship with the SDK. Each has a README that describes their contents and purpose.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2. Subdirectories for the libraries and examples RPM (continued)

| Subdirectory      | Description                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /opt/cell/sysroot | Contains the header files and libraries used during cross-compiling<br>and contains the compiled results of the libraries and examples on an<br>x86 system. The compiled libraries and examples (everything under<br>/opt/cell/sysroot/opt/cell/sdk) can be synched up with the<br>simulator system root image by using the command:<br>/opt/cell/cellsdk_sync_simulator. |

### **Performance tools**

I

Support libraries and utilities are provided by the SDK to help you with development and performance testing your Cell/B.E. applications.

For information about these libraries and tools, please refer to the *SDK Performance Guide* and the *SDK SPU Runtime Library Extensions Guide*.

## IBM Eclipse IDE for the SDK

IBM Eclipse IDE for the SDK is built upon the Eclipse and C Development Tools (CDT) platform. It integrates the GNU tool chain, compilers, the Full-System Simulator, and other development components to provide a comprehensive, Eclipse-based development platform that simplifies development.

The key features include the following:

- A C/C++ editor that supports syntax highlighting, a customizable template, and an outline window view for procedures, variables, declarations, and functions that appear in source code

- A visual interface for the PPE and SPE combined GDB (GNU debugger)

- Seamless integration of the simulator into Eclipse

- · Automatic builder, performance tools, and several other enhancements

- Remote launching, running and debugging on a IBM BladeCenter QS21

- · ALF source code templates for programming models within IDE

- An ALF Code Generator to produce an ALF template package with C source code and a readme.txt file

- A configuration option for both the Local Simulator and Remote Simulator target environments that allows you to choose between launching a simulation machine with the Cell/B.E. processor or an enhanced CBEA-compliant processor with a fully pipelined, double precision SPE processor

- Remote Cell/B.E. and simulator BladeCenter support

- SPU timing integration

- PDT integration

- · Automatic makefile generation for both GCC and XLC projects

For information about how to install and remove the IBM Eclipse IDE for the SDK, see the *SDK Installation Guide*.

For information about using the IDE, an online tutorial is available. The IDE and related programs must be installed before you can access the tutorial. The tutorial is also available as a section in the *SDK IDE Tutorial and User's Guide*.

## Overview of the hybrid programming environment

The Cell Broadband Engine Architecture (CBEA) is an example of a multi-core hybrid system on a chip.

That is to say, heterogeneous cores integrated on a single processor with an inherent memory hierarchy. Specifically, the synergistic processing elements (SPEs) can be thought of as computational accelerators for a more general purpose PPE core. These concepts of hybrid systems, memory hierarchies and accelerators can be extended more generally to coupled I/O devices, and examples of those systems exist today, for example, GPUs in PCIe slots for workstations and desktops. Similarly, the Cell/B.E. processors is being used in systems as an accelerator, where computationally intensive workloads well suited for the CBEA are off-loaded from a more standard processing node. There are many ways to move data and functions from a host processor to an accelerator processor and vice versa.

To provide a consistent methodology and set of application programming interfaces (APIs) for a variety of hybrid systems, including the Cell/B.E. SoC hybrid system, the SDK has implementations of the Cell/B.E. multi-core data communication and programming model libraries, Data and Communication Synchronization (DaCS) and Accelerated Library Framework (ALF), which can be used on x86/Linux host process systems with Cell/B.E.-based accelerators. A prototype implementation over sockets is provided so that you can gain experience with this programming style and focus on how to manage the distribution of processing and data decomposition. For example, in the case of hybrid programming when moving data point to point over a network, care must be taken to maximize the computational work done on accelerator nodes potentially with asynchronous or overlapping communication, given the potential cost in communicating input and results.

For more information about the DaCS programming APIs, refer to the Data and Communication Synchronization Library Programmer's Guide and API Reference.

For more information about the ALF programming APIs, refer to the Accelerated Library Framework Programmer's Guide and API Reference.

Т

Т

T

T

## Chapter 2. Programming with the SDK

This section is a short introduction about programming with the SDK.

It covers the following topics:

- "SDK directories"

- "Specifying the processor architecture"

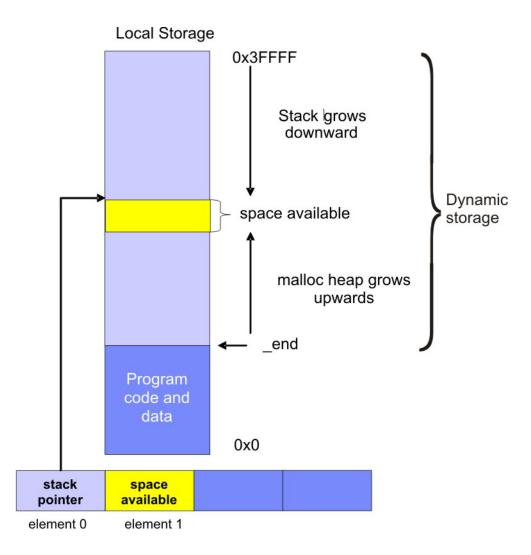

- "SPU stack analysis" on page 27

- "SDK programming examples and demos" on page 15

- "Using the huge translation lookaside buffer (TLB) to reserve memory" on page 20

- "Developing applications with the SDK" on page 17

- "Performance considerations" on page 20

Refer to the *Cell/B.E. Programming Tutorial*, and other documentation for more details.

## **SDK directories**

Because of the cross-compile environment in the SDK, there are several different system root directories.

Table 3 describes these directories.

Table 3. System root directories

| Directory name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host                   | The system root for the host system is "/". The SDK is installed relative to this host system root.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GCC Toolchain          | The system root for the GCC tool chain depends on the host<br>platform. For PPC platforms including the IBM BladeCenter<br>QS21, this directory is the same as the host system root. For<br>x86 and x86-64 systems this directory is /opt/cell/sysroot.<br>The tool chain PPU header and library files are stored relative<br>to the GCC Tool chain system root in directories such as<br>usr/include and usr/lib. The tool chain SPU header and<br>library files are stored relative to the GCC Toolchain system<br>root in directories such as usr/spu/include and usr/spu/lib. |

| Examples and Libraries | The Examples and Libraries system root directory is<br>/opt/cell/sysroot. When the samples and libraries are<br>compiled and linked, the resulting header files, libraries and<br>binaries are placed relative to this directory in directories such<br>as usr/include, usr/lib, and /opt/cell/sdk/usr/bin. The<br>libspe library is also installed into this system root.                                                                                                                                                                                                        |

## Specifying the processor architecture

Many of the tools provided in SDK support multiple implementations of the CBEA.

These include the Cell/B.E. processor and the PowerXCell 8i processor. The PowerXCell 8i processor is a CBEA-compliant processor with a fully pipelined, enhanced double precision SPU.

The processor supports five optional instructions to the SPU Instruction Set Architecture. These include:

- DFCEQ

- DFCGT

- DFCMEQ

- DFCMEQ

- DFCMGT

Detailed documentation for these instructions is provided in version 1.2 (or later) of the *Synergistic Processor Unit Instruction Set Architecture specification*. The PowerXCell 8i processor also supports improved issue and latency for all double precision instructions.

The SDK compilers support compilation for either the Cell/B.E. processor or the PowerXCell 8i processor.

| Options                      | Description                                                                                                                                                                                                                     |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -march=< <i>cpu type&gt;</i> | Generate machine code for the SPU architecture specified by<br>the CPU type. Supported CPU types are either cell (default)<br>or celledp, corresponding to the Cell/B.E. processor or<br>PowerXCell 8i processor, respectively. |  |

| -mtune=< <i>cpu type</i> >   | Schedule instructions according to the pipeline model of the specified CPU type. Supported CPU types are either cell (default) or celledp, corresponding to the Cell/B.E. processor or PowerXCell 8i processor, respectively.   |  |

Table 4. spu-gcc compiler options

Table 5. spu-xlc compiler options

| Option                     | Description                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -qarch=< <i>cpu type</i> > | Generate machine code for the SPU architecture specified by<br>the CPU type. Supported CPU types are either spu (default)<br>or edp, corresponding to the Cell/B.E. processor or<br>PowerXCell 8i processor, respectively. |

| -qtune=< <i>cpu type</i> > | Schedule instructions according to the pipeline model of the specified CPU type. Supported CPU types are either spu (default) or edp, corresponding to the Cell/B.E. processor or PowerXCell 8i processor, respectively.   |

The static timing analysis tool, spu\_timing, also supports multiple processor implementations. The command line option -march=celledp can be used to specify that the timing analysis be done corresponding to the PowerXCell 8i processors' enhanced pipeline model. If the architecture is unspecified or invoked with the command line option -march=cell, then analysis is done corresponding to the Cell/B.E. processor's pipeline model.

## SDK programming examples and demos

Each of the examples and demos has an associated README.txt file. There is also a top-level readme in the /opt/cell/sdk/src directory, which introduces the structure of the example code source tree.

Almost all of the examples run both within the simulator and on the IBM BladeCenter QS21 and IBM BladeCenter QS22. Some examples include SPU-only programs that can be run on the simulator in standalone mode.

The source code, which is specific to a given Cell/B.E. processor unit type, is in the corresponding subdirectory within a given example's directory:

- ppu for code compiled to run on the PPE

- ppu64 for code specifically compiled for 64-bit ABI on the PPE

- spu for code compiled to run on an SPE

- spu\_sim for code compiled to run on an SPE under the system simulator in

standalone environment

## Overview of the build environment

In /opt/cell/sdk/buildutils there are some top level Makefiles that control the build environment for all of the examples.

Most of the directories in the libraries and examples contain a Makefile for that directory and everything below it. All of the examples have their own Makefile but the common definitions are in the top level Makefiles.

The build environment Makefiles are documented in /opt/cell/sdk/buildutils/ README\_build\_env.txt.

## Changing the build environment

Environment variables in the /opt/cell/sdk/buildutils/make.\* files are used to determine which compiler is used to build the examples.

| <br> | <b>Note:</b> These environment variables and scripts ONLY work for Makefile examples that use the make.footer provided by the SDK. Other Makefiles may not be affected by these actions. |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br> | The /opt/cell/sdk/buildutils/cellsdk_select_compiler script can be used to switch the compiler. The syntax of this command is:                                                           |

| I    | <pre>/cell/sdk:/opt/cell/sdk/buildutils/cellsdk_select_compiler -?</pre>                                                                                                                 |

|      | Usage: cellsdk_select_compiler <gcc gfortran="" gnu="" xl="" xlc="" xlf=""  =""> where:</gcc>                                                                                            |